从晶体管到系统封装:TSMC定义CMOS缩放的新逻辑

引言

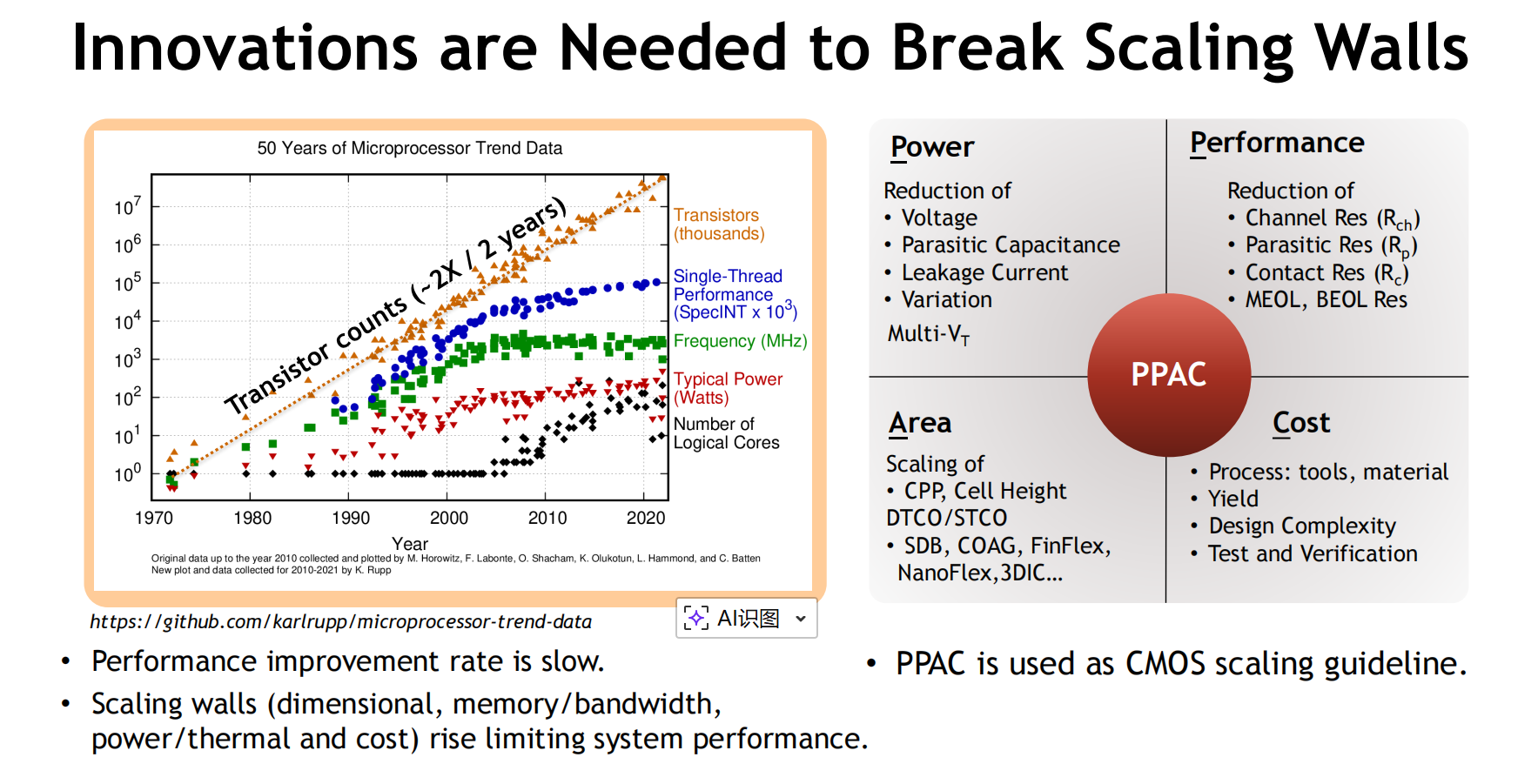

过去半个世纪,CMOS技术沿着摩尔定律轨迹高速演进,推动了全球数字基础设施的指数级扩张。然而,随着Dennard Scaling失效与晶体管物理极限临近,传统“线宽缩小即进步”的范式正在失去主导地位。功耗、性能、面积与成本(PPAC)之间的权衡愈发复杂,推动产业从“单点缩放”转向“系统协同”。在此背景下,本报告由TSMC在2025年VLSI技术研讨会上发布,全面梳理了CMOS逻辑缩放的技术趋势、设计挑战与系统级集成路径,并通过丰富的技术节点实证与架构分析,描绘出未来逻辑工艺从FinFET、Nanosheet到CFET的演进脉络,以及DTCO与STCO双轮驱动下的新一代系统优化策略。

一、摩尔定律的持续驱动与晶体管演进

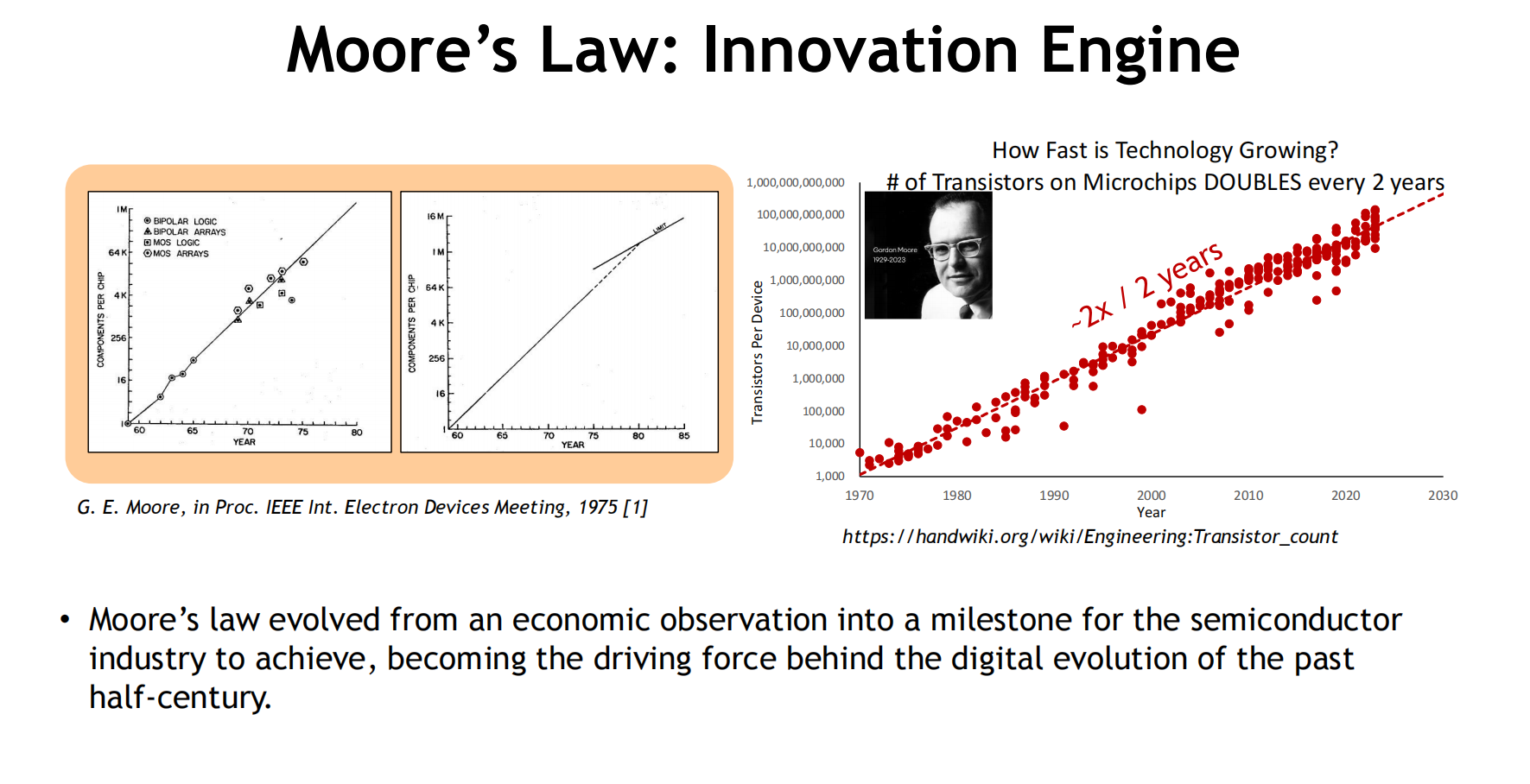

摩尔定律的提出,最初只是对集成电路经济性的经验观察。如今,它早已成为全球半导体产业自我加压与技术突破的标尺。过去半个世纪中,摩尔定律推动晶体管数量以每两年翻倍的速度增长,成为数字化浪潮的根基。

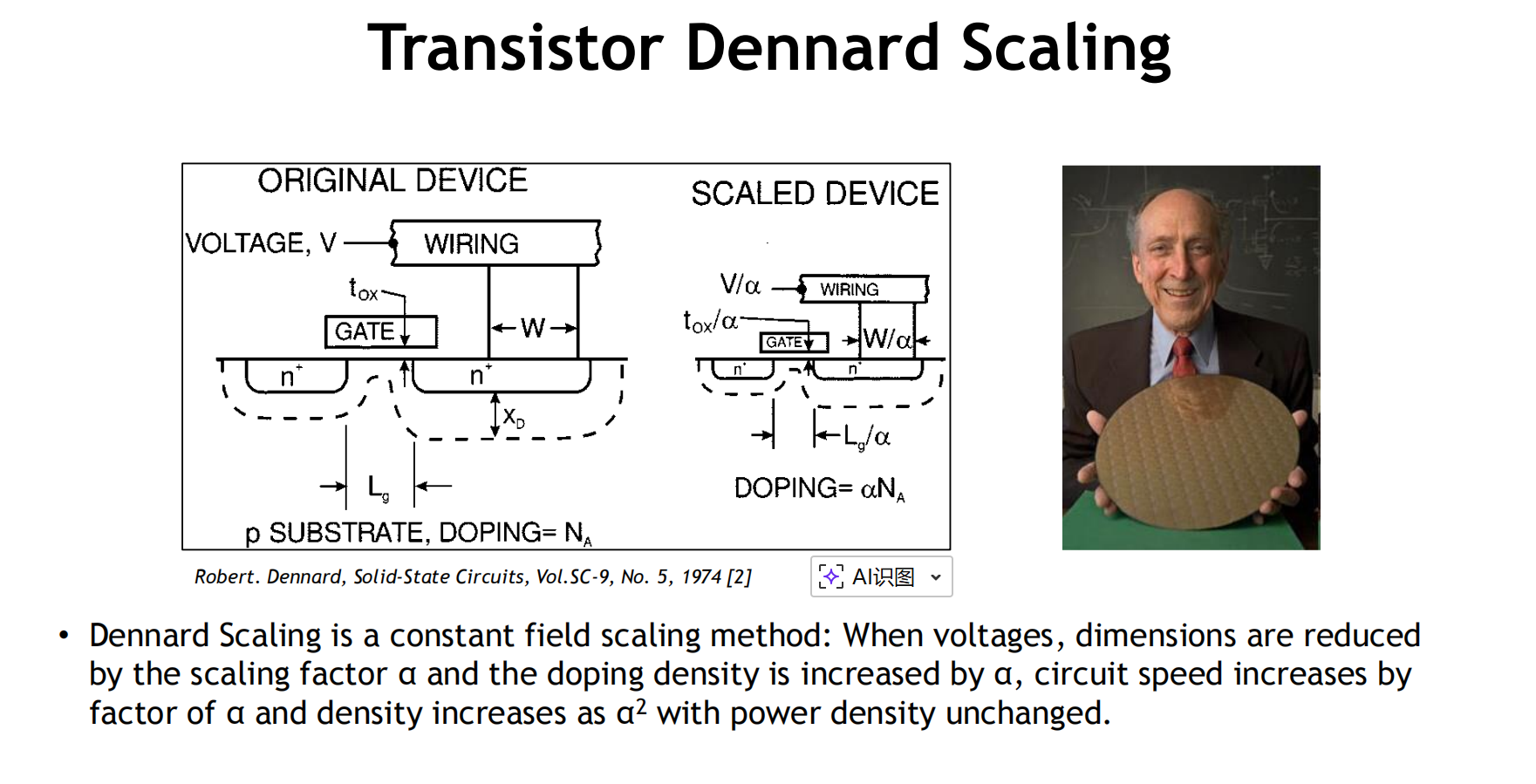

然而,传统的Dennard Scaling所依赖的等场缩放(constant field scaling)机制早已走到尽头。随着电压不再按比例下降,功耗密度不再恒定,器件热效应和能效瓶颈相继浮出水面。进入后Dennard时代,晶体管缩放面临四大“墙”:尺寸、带宽、功耗与成本,正在共同重塑CMOS的演进逻辑。

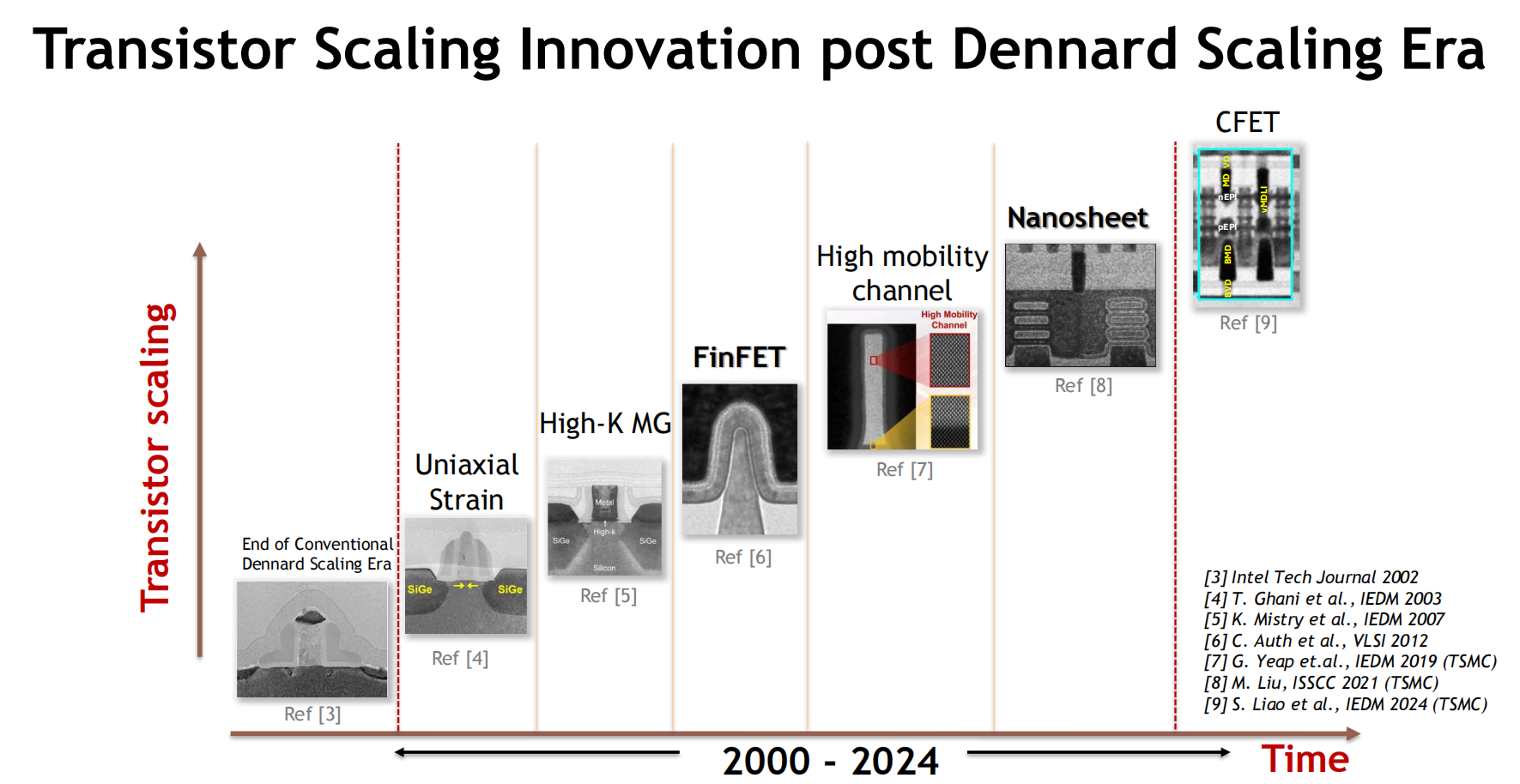

为应对物理极限的逼近,晶体管结构创新成为突破路径。从应变硅、High-k金属栅(HKMG)到FinFET,再到当前的Nanosheet与前沿的CFET,每一次架构飞跃,背后都是设计、电学、热学与制造的系统性突破。

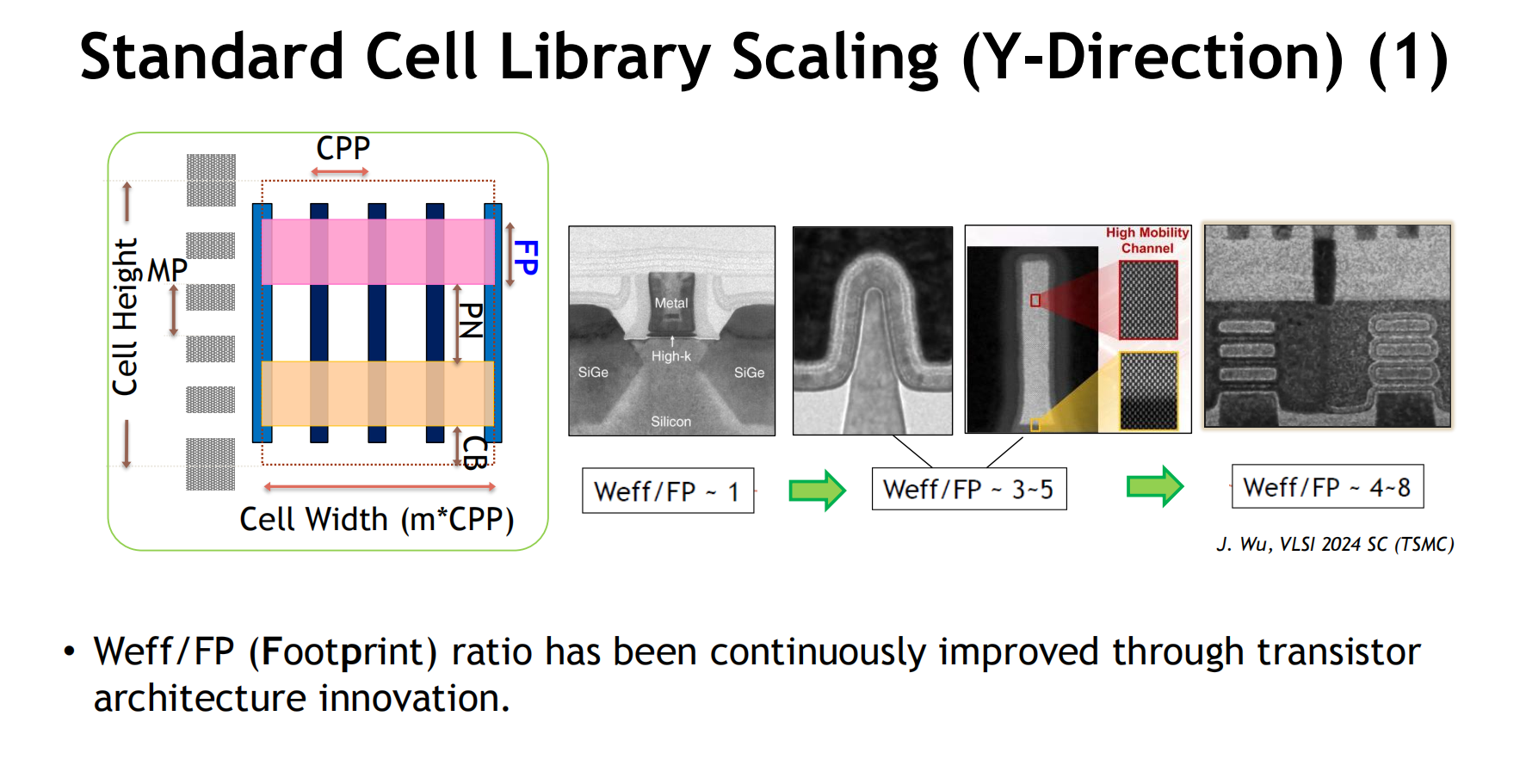

FinFET的三维结构提升了短沟道控制,延续了多个节点的缩放周期。而Nanosheet(NS)通过引入栅极全环绕(GAA)结构,不仅进一步改善静电控制,还带来更高的Weff/FP比值,为高性能低功耗应用提供了全新设计自由度。如今,GAA结构已成为先进逻辑制程的主流架构之一。

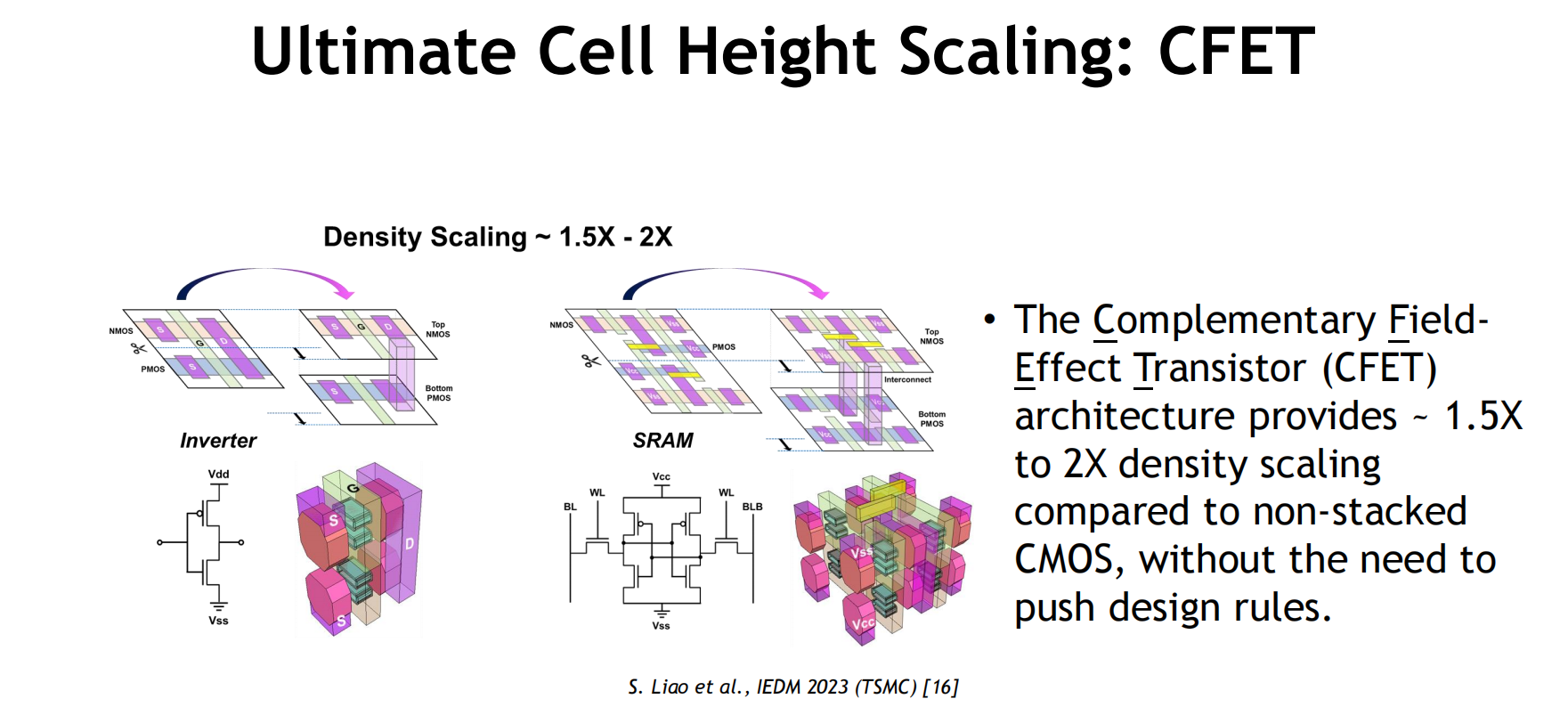

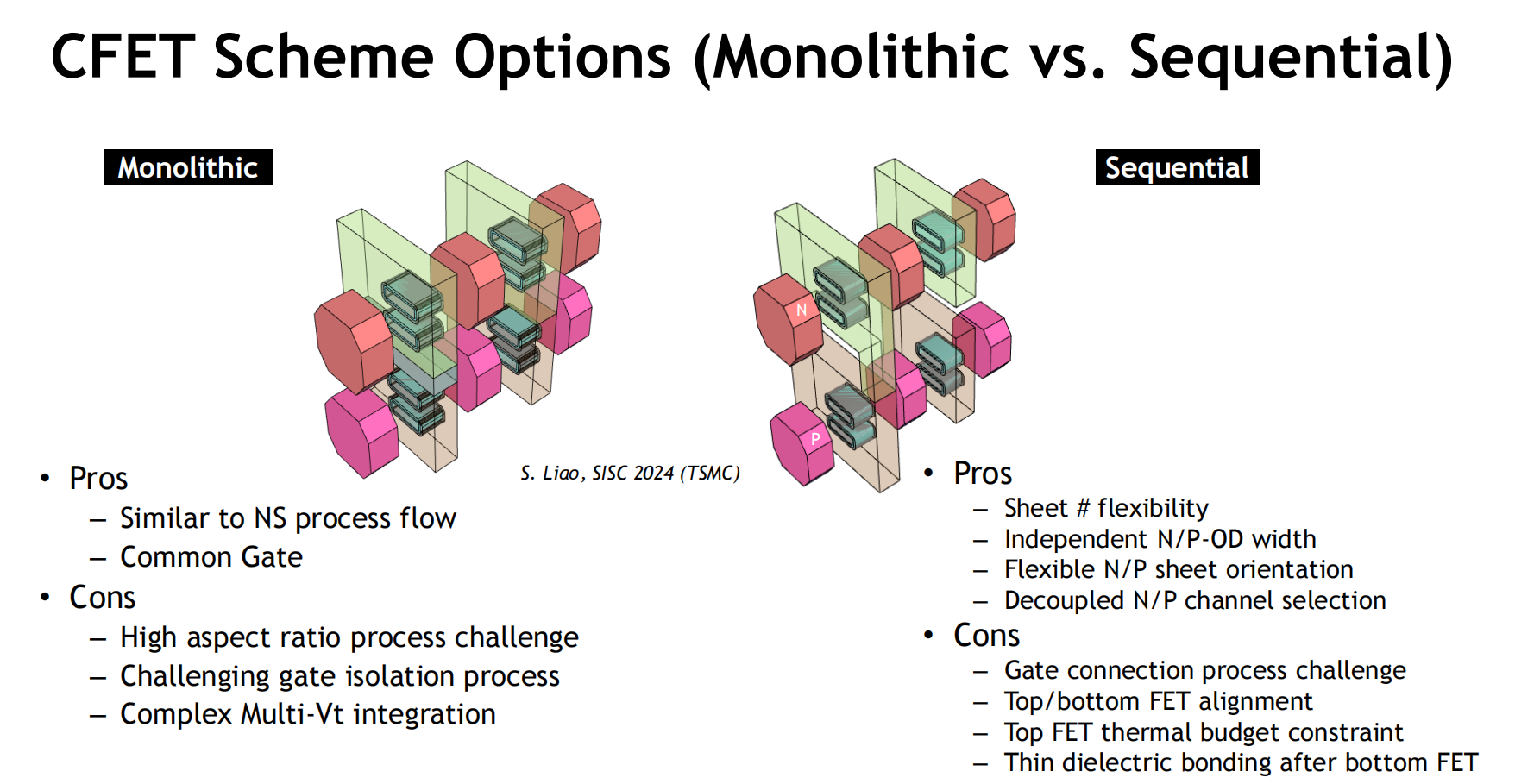

而CFET的出现,则堪称CMOS架构的一次范式转变。通过将PMOS和NMOS沿垂直方向堆叠,CFET可在不推高设计规则的情况下实现1.5–2倍的晶体管密度提升,其对布局面积的“解耦”特性,标志着CMOS缩放从“平面紧凑”走向“空间叠层”的新时代。

结构创新虽是硬核路径,但仍需辅以系统协同的策略支撑。PPAC(Power, Performance, Area, Cost)已取代单一“技术节点”成为行业新坐标。在“性能不再自动提升”的现实下,缩放的定义被重构:不是线宽变窄,而是能否用最优资源组合,实现最优PPAC。

二、逻辑CMOS缩放的核心技术演进

逻辑单元的几何尺寸缩放,是CMOS技术演进的基础之一。今天的晶体管尺寸早已突破传统物理极限,但仍在以架构重构与协同优化的方式,持续推进密度、性能与功耗之间的平衡。

横向缩放:CPP演进路径

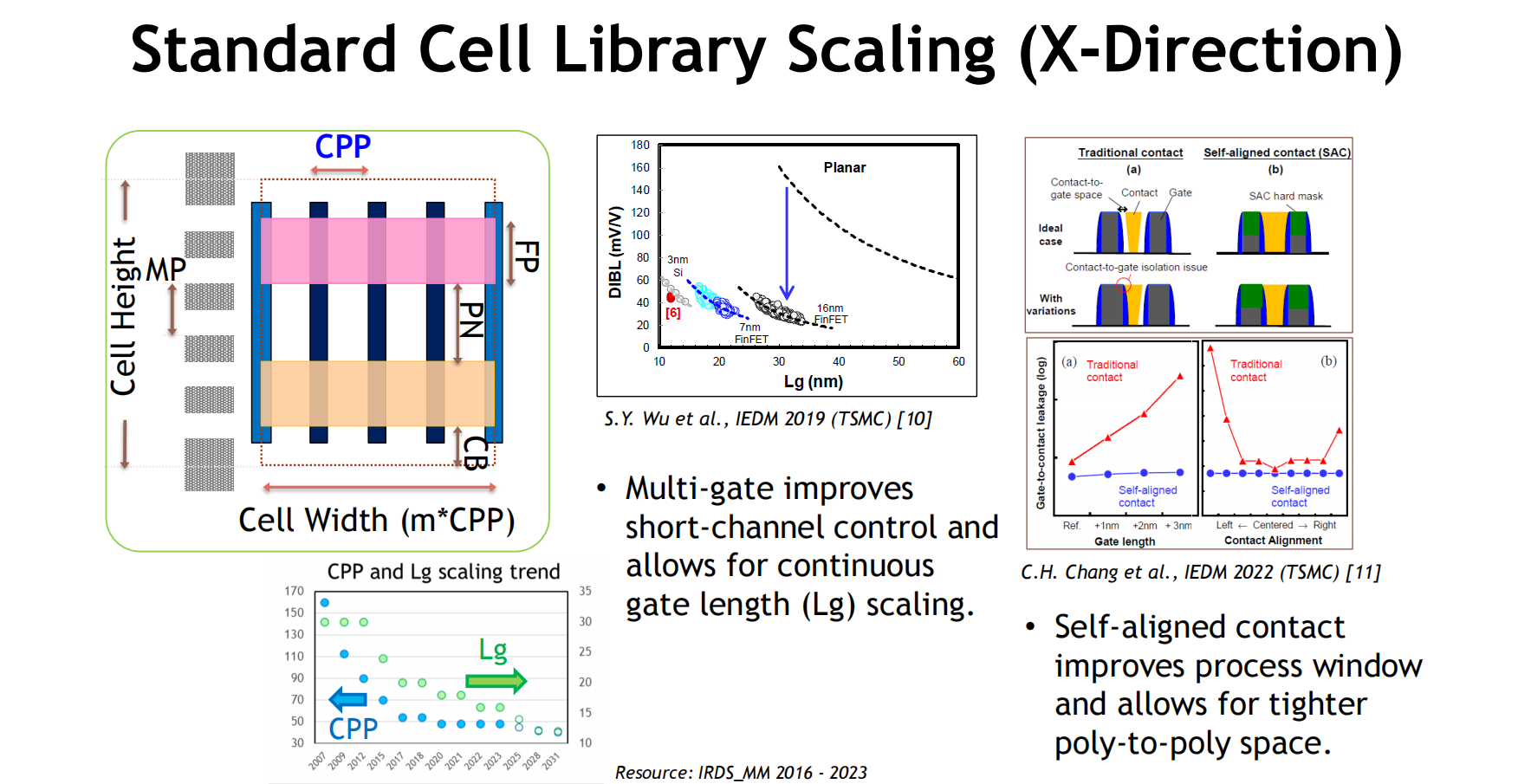

在标准单元的X方向(横向),CPP(Contacted Poly Pitch)是决定栅极间距与密度的核心参数。通过引入多栅结构与自对准接触技术,行业成功实现在不断缩小Lg(栅长)的同时,维持良好的短沟道控制能力。

自对准接触(SAC)的应用,显著提升了工艺窗口,缩短了Poly-to-Poly间距,使栅极间距进一步压缩成为可能。多代技术报告显示,SAC是驱动CPP从90nm级别逼近50nm以下的关键节点工艺之一。

纵向缩放:Cell Height与Backside Power架构

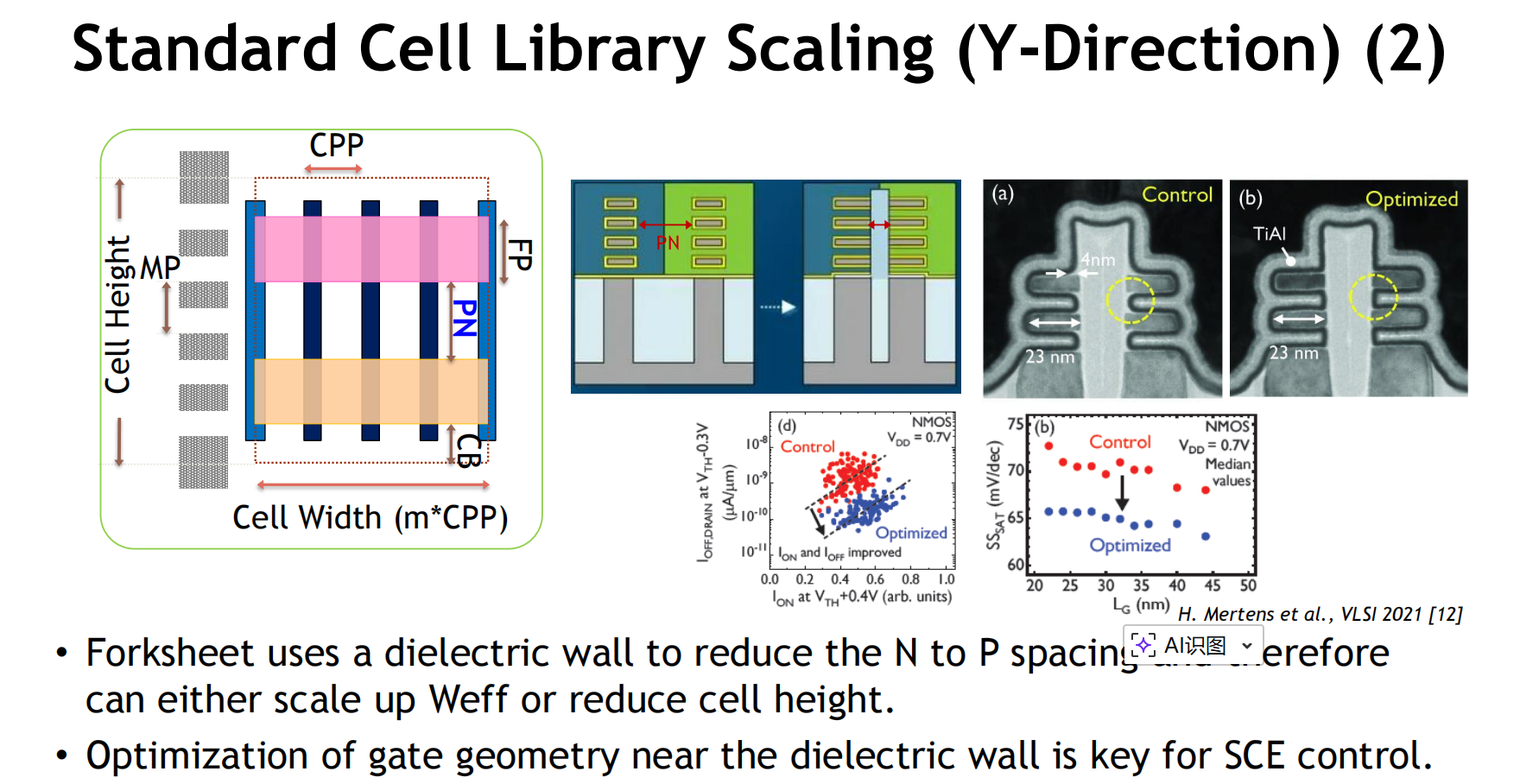

Y方向缩放的核心在于缩小Metal Pitch(MP)与Cell Height。随着工艺复杂性上升,金属线宽与间距已难以线性缩减,出现RC性能劣化与制造成本剧增等问题。Forksheet架构的提出,利用中间介电墙(dielectric wall)有效减小N/P间距,从而在保持驱动能力的同时压低单元高度。

此外,Super Power Rail与Backside Power Delivery Network(BSPDN)等背面供电方案,也成为缓解前端供电拥塞、提升电源完整性与布线效率的关键创新。在2024年TSMC技术研讨会上,BSPDN已明确作为未来制程标准化方向之一。

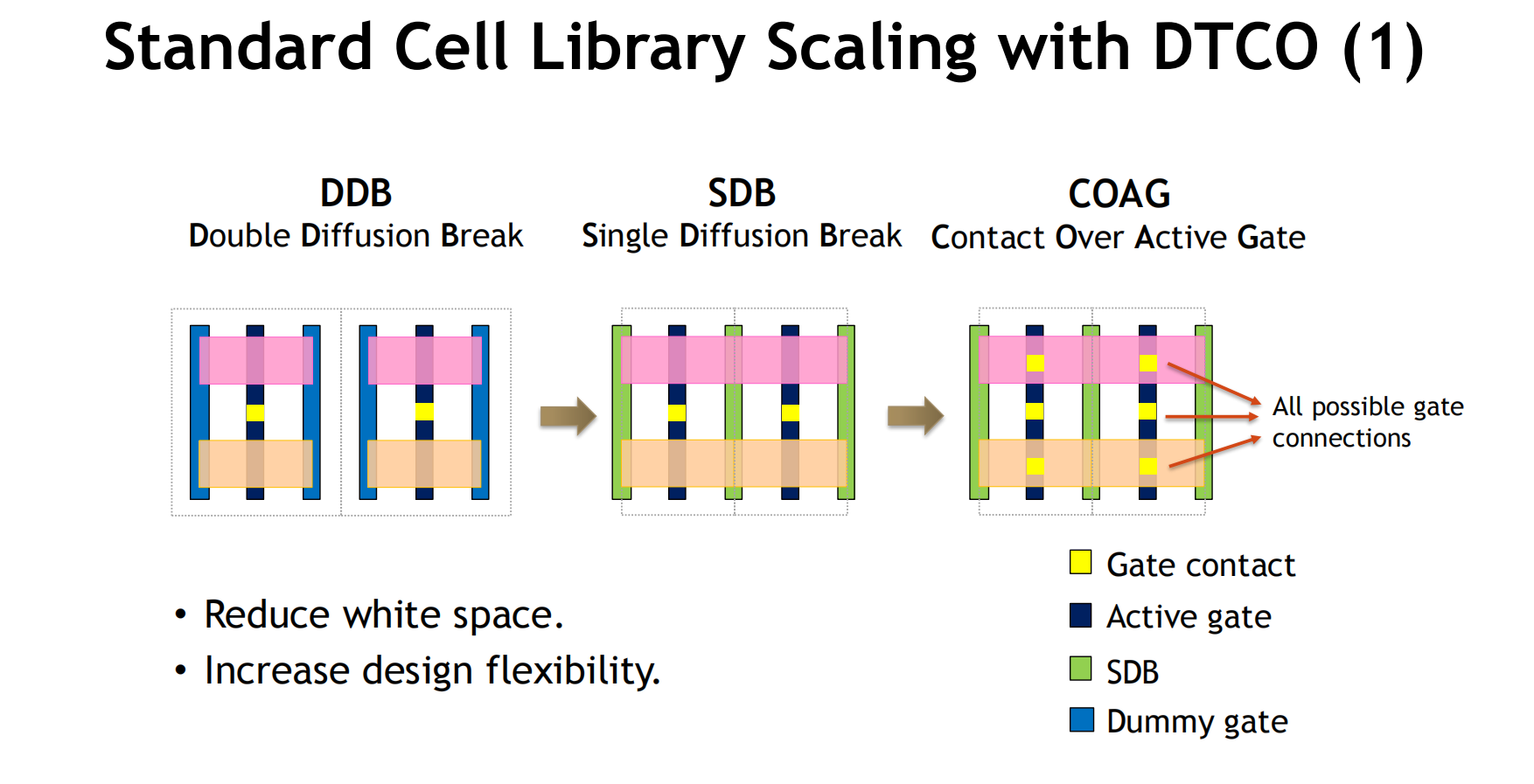

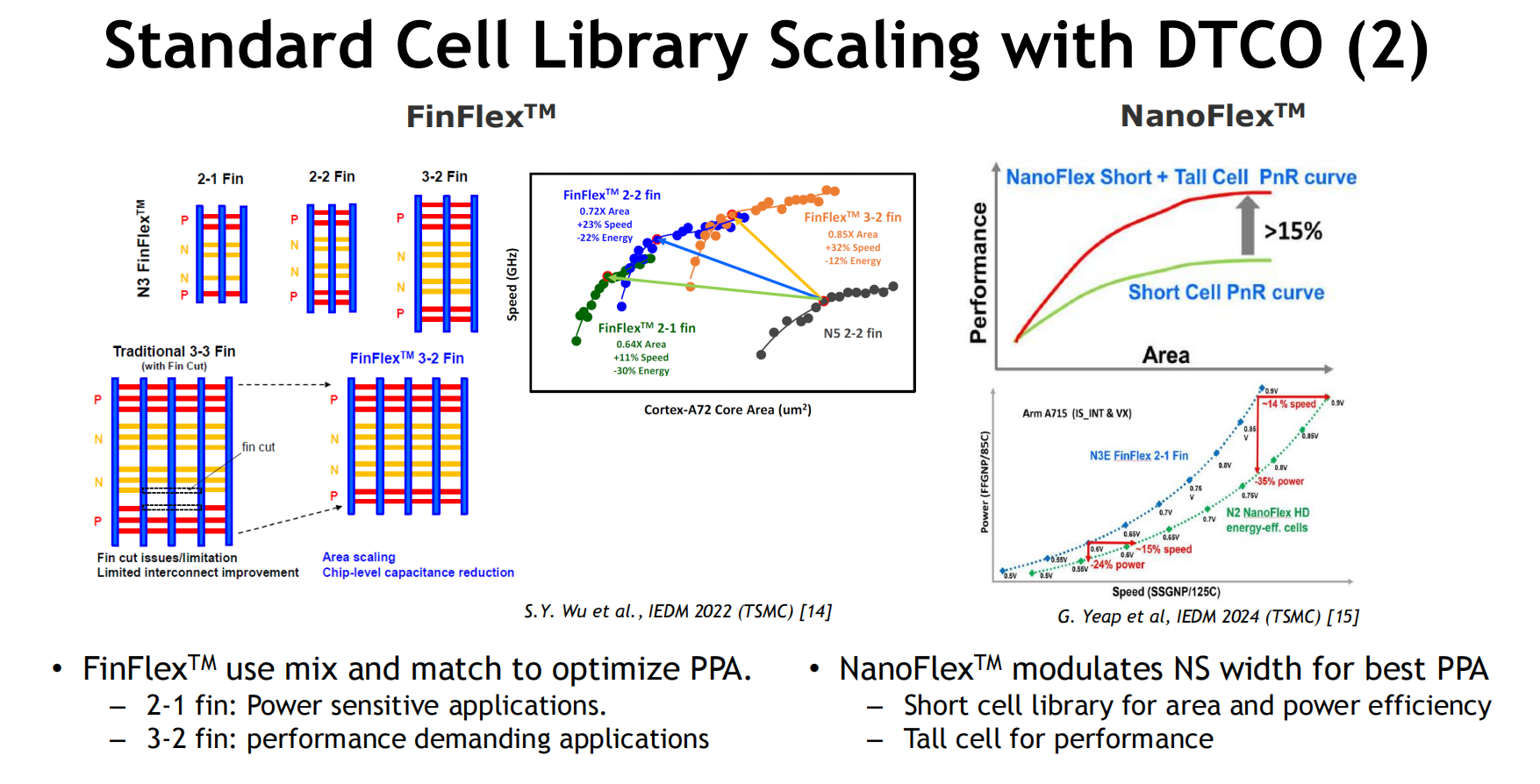

DTCO导向创新:SDB、COAG与FinFlex/NanoFlex

面对传统标准单元布局在高密度节点下的效率瓶颈,设计与工艺深度融合(DTCO)成为破局关键。

·SDB(Single Diffusion Break)与COAG(Contact Over Active Gate)通过最小化白区(whitespace)与提升接触布线效率,实现更高的利用率与灵活度。

·FinFlex™ 提供2-1、3-2等Fin组合,使设计在功耗敏感与性能导向之间灵活切换;NanoFlex™则进一步通过Nanosheet宽度调控,实现短单元与长单元之间的面积与性能权衡,极大丰富了单元库的优化空间。

这些技术的本质,是将PPA优化权下放到设计层,赋予芯片架构师更高维度的自由度与差异化空间。

CFET:突破密度极限的架构解法

当平面与高度缩放空间均趋于极限,CFET应运而生。通过垂直堆叠PMOS与NMOS,CFET可在相同面积下实现高达2倍的单元密度提升,且不需牺牲设计规则容差或引入更激进的掺杂控制。

其实现路径分为Monolithic与Sequential两类架构:

·Monolithic CFET因其接近NS工艺流程、共享栅极等优势而便于整合;

·Sequential CFET则通过上下片段独立构建,提供更高灵活度,但挑战在于层间对准、热预算限制与接触结构复杂化。

密度已不仅来自平面压缩,而是源自三维堆叠下的结构重构能力。

三、极限缩放下的性能与功耗控制策略

当晶体管尺寸已趋物理极限,性能与功耗的优化,不再是单点突破问题,而演化为全链路的系统性工程。极限工艺节点下,每一纳安、每一飞法、每一原子层的优化,都关乎逻辑性能的最终天花板。

功耗解析:三类功耗协同压降

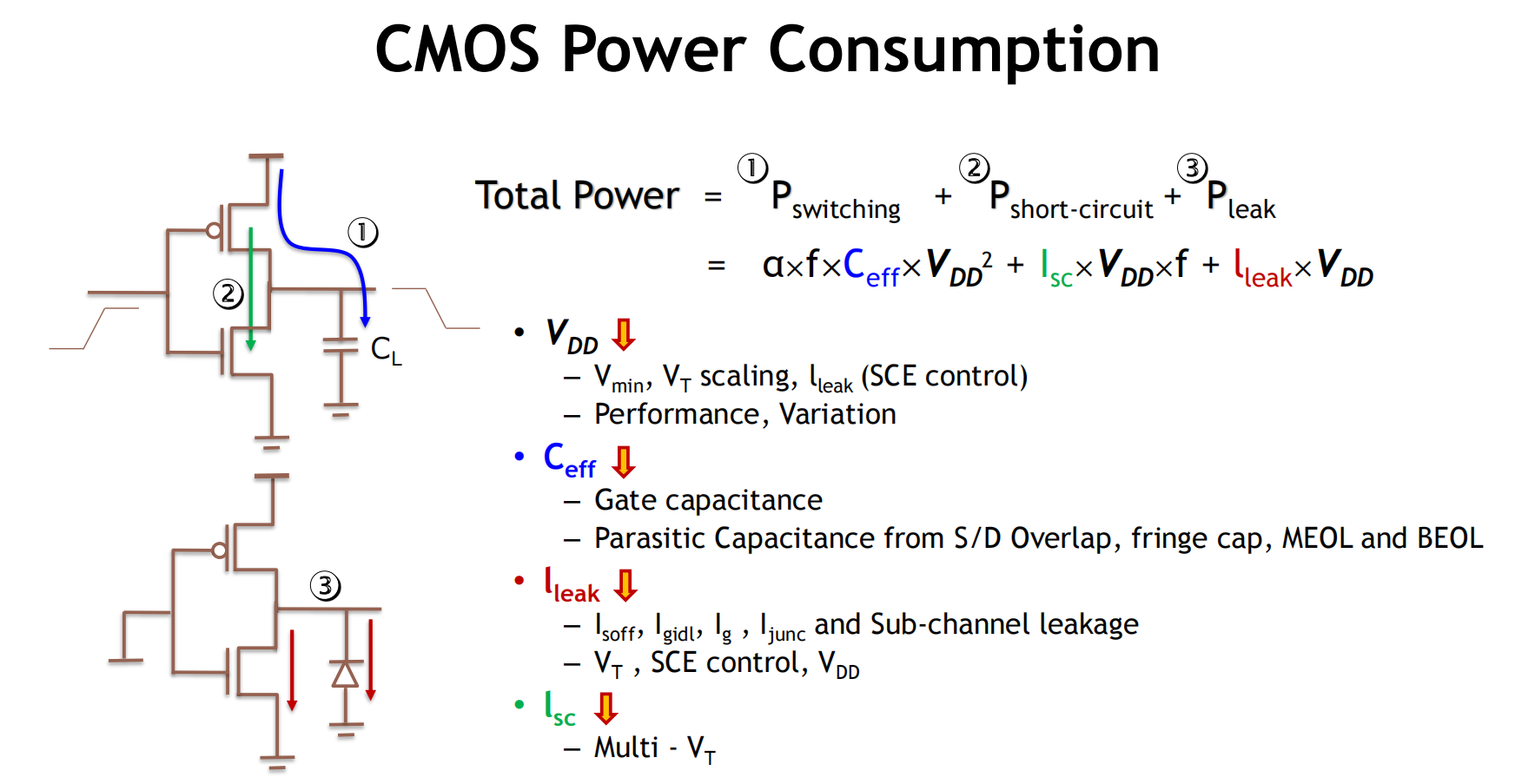

CMOS电路的总功耗由三部分组成:

·切换功耗(Pswitching):与频率、Ceff和VDD平方成正比

·短路功耗(Psc):主要受开关过程中的瞬时电流影响

·漏电功耗(Pleak):由静态漏电流决定,VDD越低越敏感

等式:Ptotal = αfCeffVDD² + Isc×VDD×f + Ileak×VDD

其中,Ceff、VDD与Ileak正是现代工艺中PPA权衡的三角平衡点。每一次VDD下探,都需同步控制静态漏电与电压波动对性能的影响。

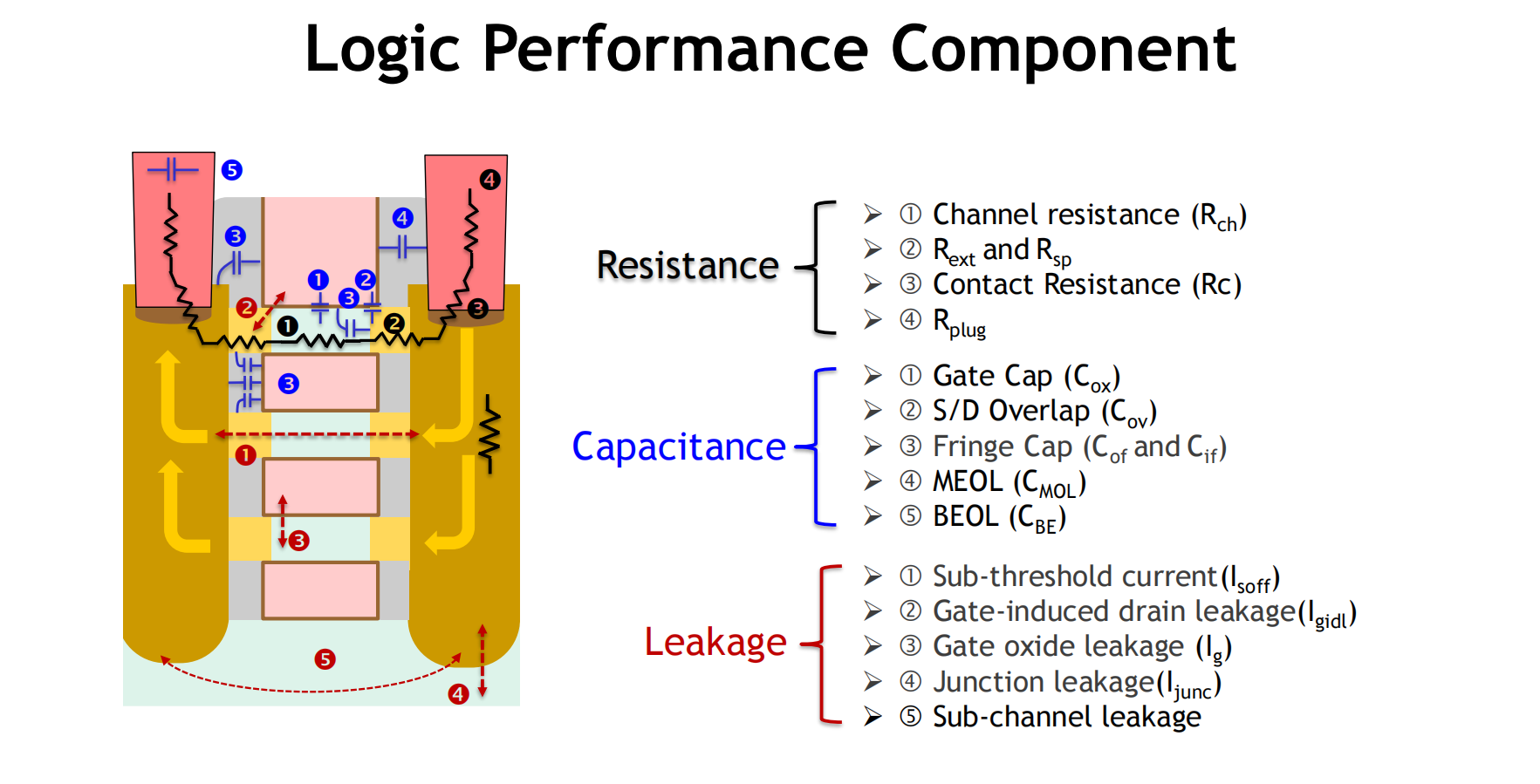

性能限制:电阻、电容、泄漏三大瓶颈

逻辑性能在物理层面主要受限于三类因素:

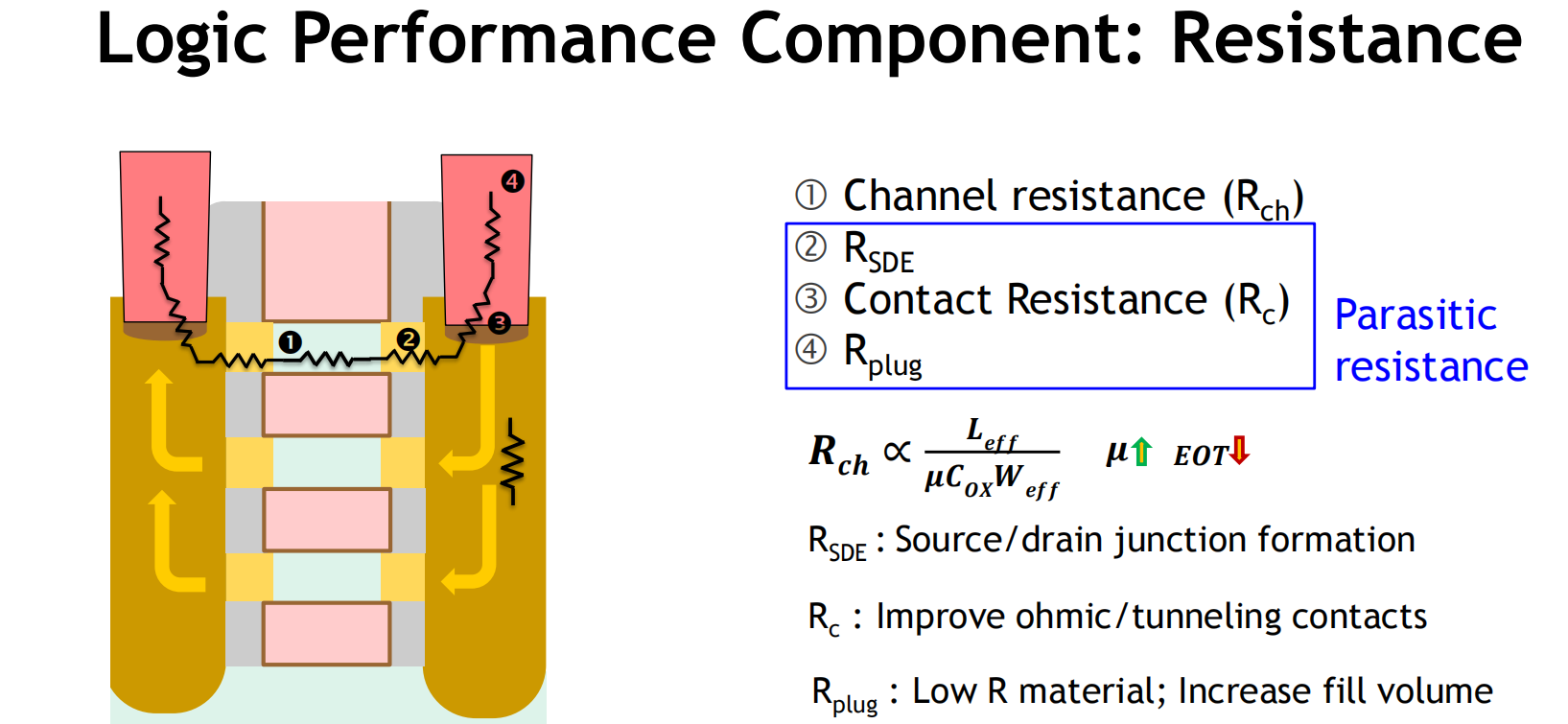

1.电阻链路:包括沟道电阻(Rch)、接触电阻(Rc)、接插件电阻(Rplug)等,Rch ∝ Leff / (μCoxWeff),在极小Leff下极易抬升。

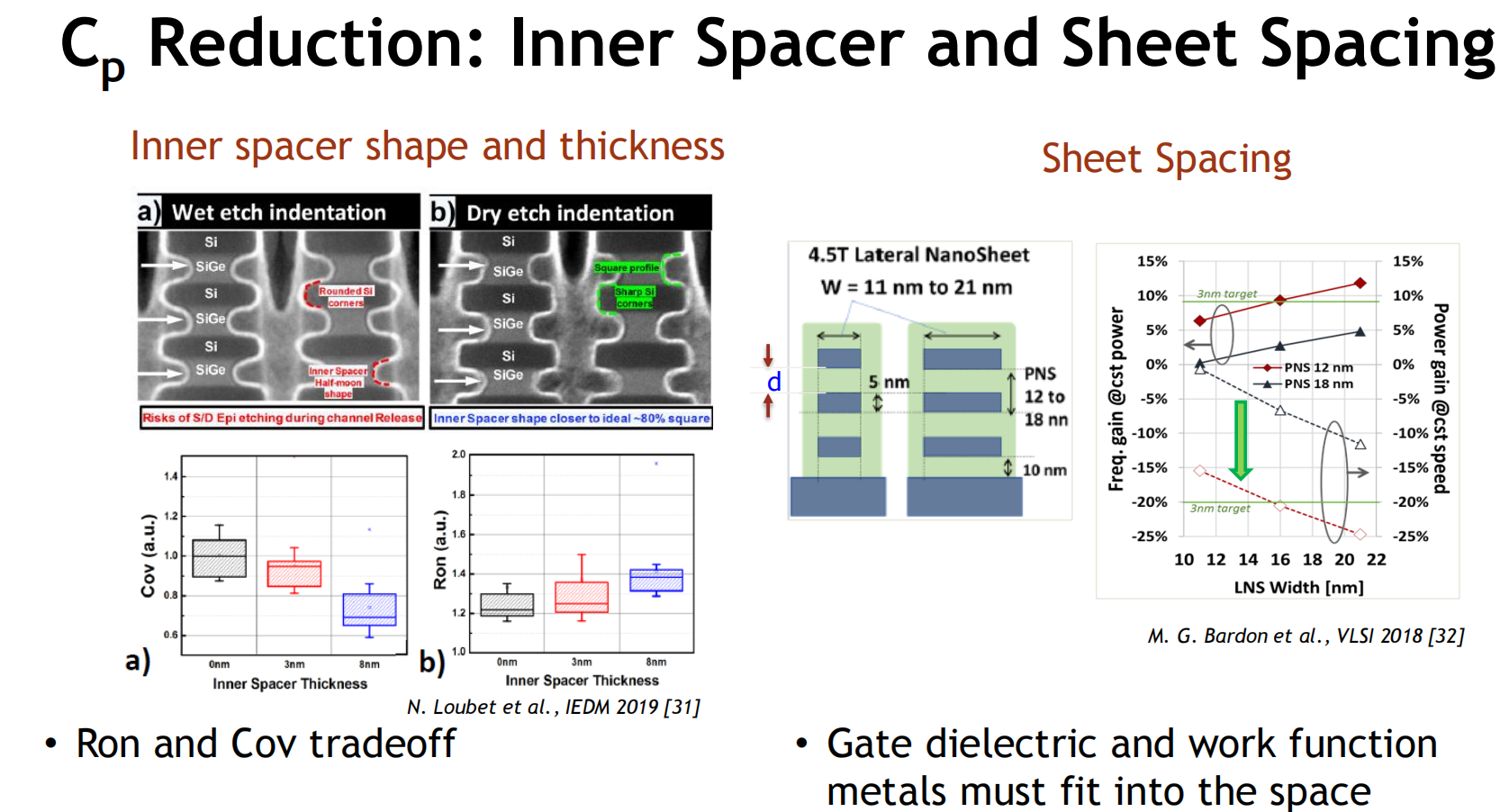

2.寄生电容:来自源漏重叠、电栅边缘电容(Cof)、中介(MEOL)与金属层间(BEOL)寄生,影响切换延迟和能耗。

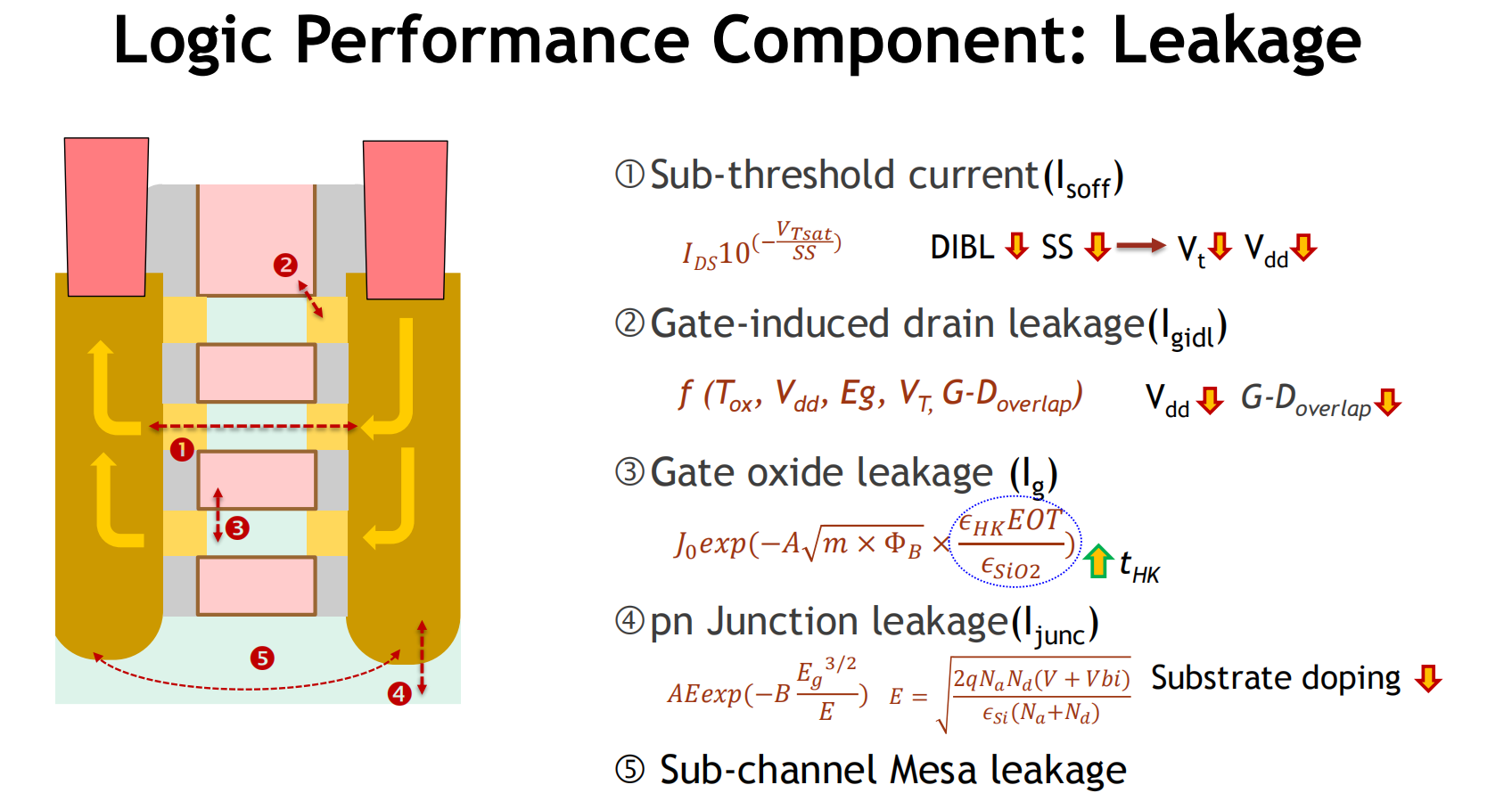

3.漏电路径:Isoff、Igidl、Gate leakage、Junction leakage与Sub-channel leakage构成了极限工艺中泄漏电流的主要来源。

在2nm以下节点,电阻与电容的每一细微变化,都会直接映射为频率或能效的非线性回报递减。

材料与结构优化:从源极到接触的全链路革新

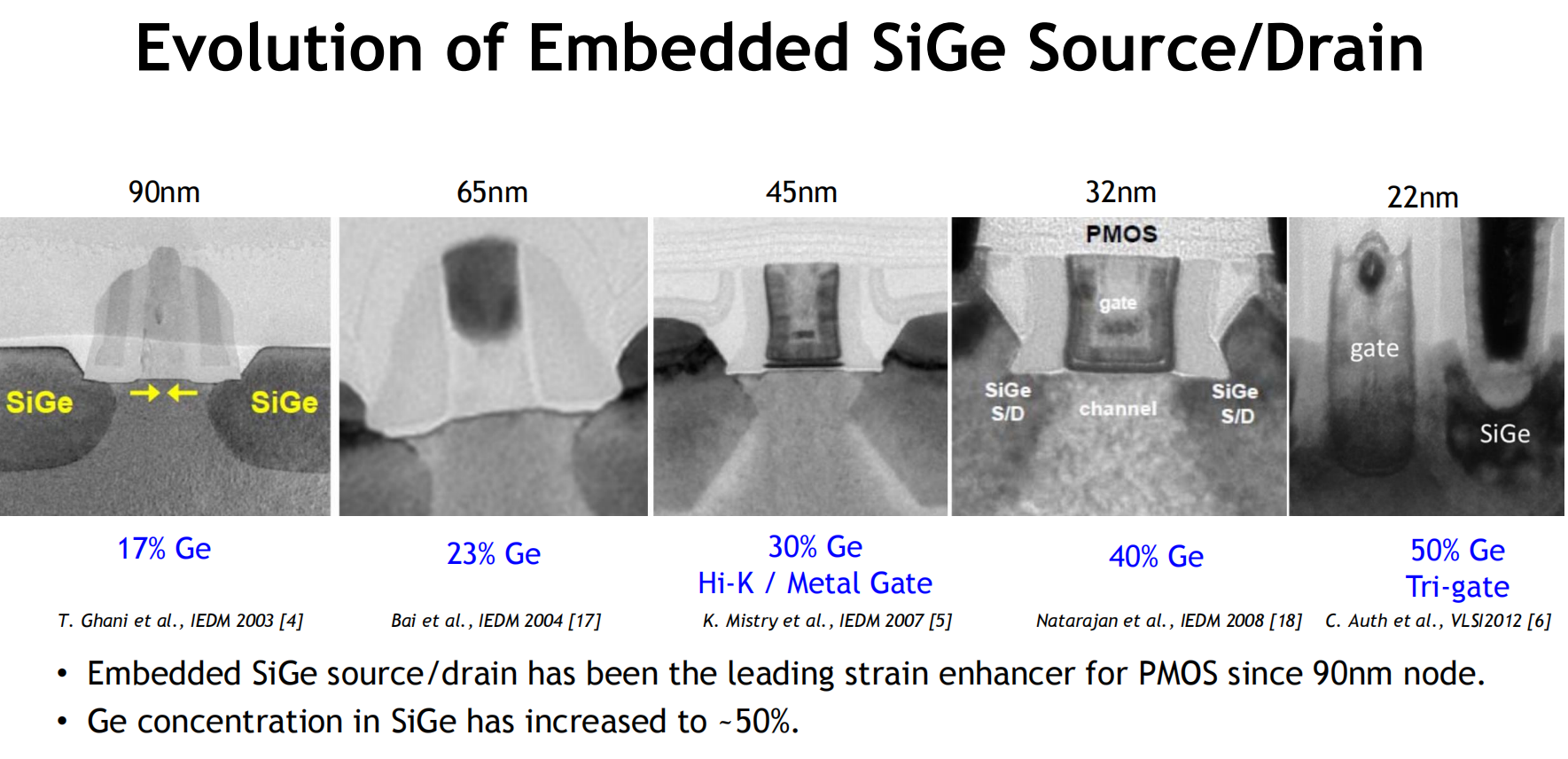

• 应变增强:eSiGe与应变Si通道

eSiGe作为PMOS应变增强的主流方案,其Ge浓度已从90nm节点的17%,上升至22nm节点的50%。但在3D结构中,eSiGe容易在内间隔处融合缺陷,降低应变传递效率,需更精细的外延与掺杂控制。

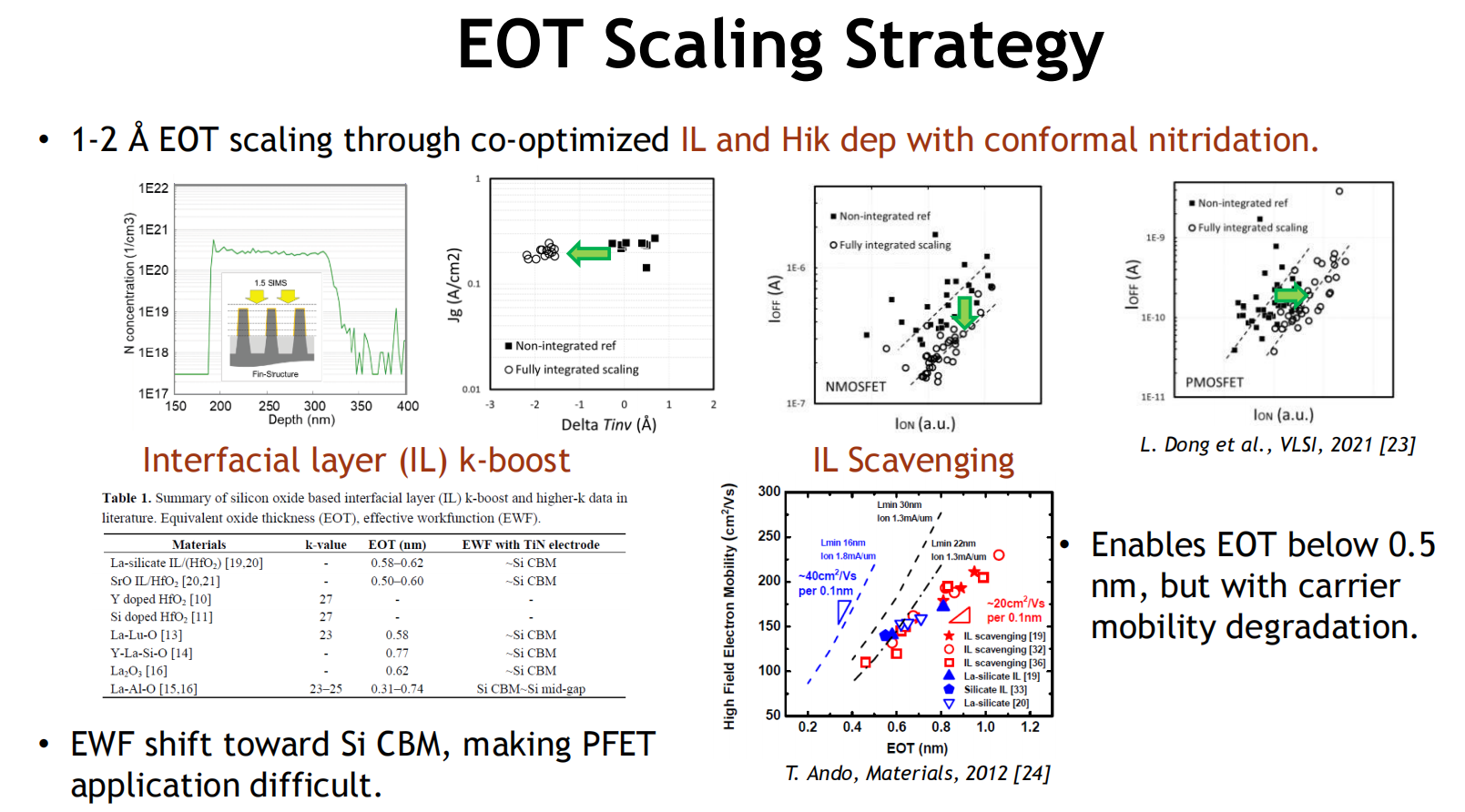

• 极限EOT(等效氧化层厚度)控制

通过界面层掺杂与高k堆叠的协同沉积,EOT现已被压缩至<0.5nm 量级,但同时带来载流子迁移率下降与功函数工程挑战,尤其对PFET设计提出新材料需求。

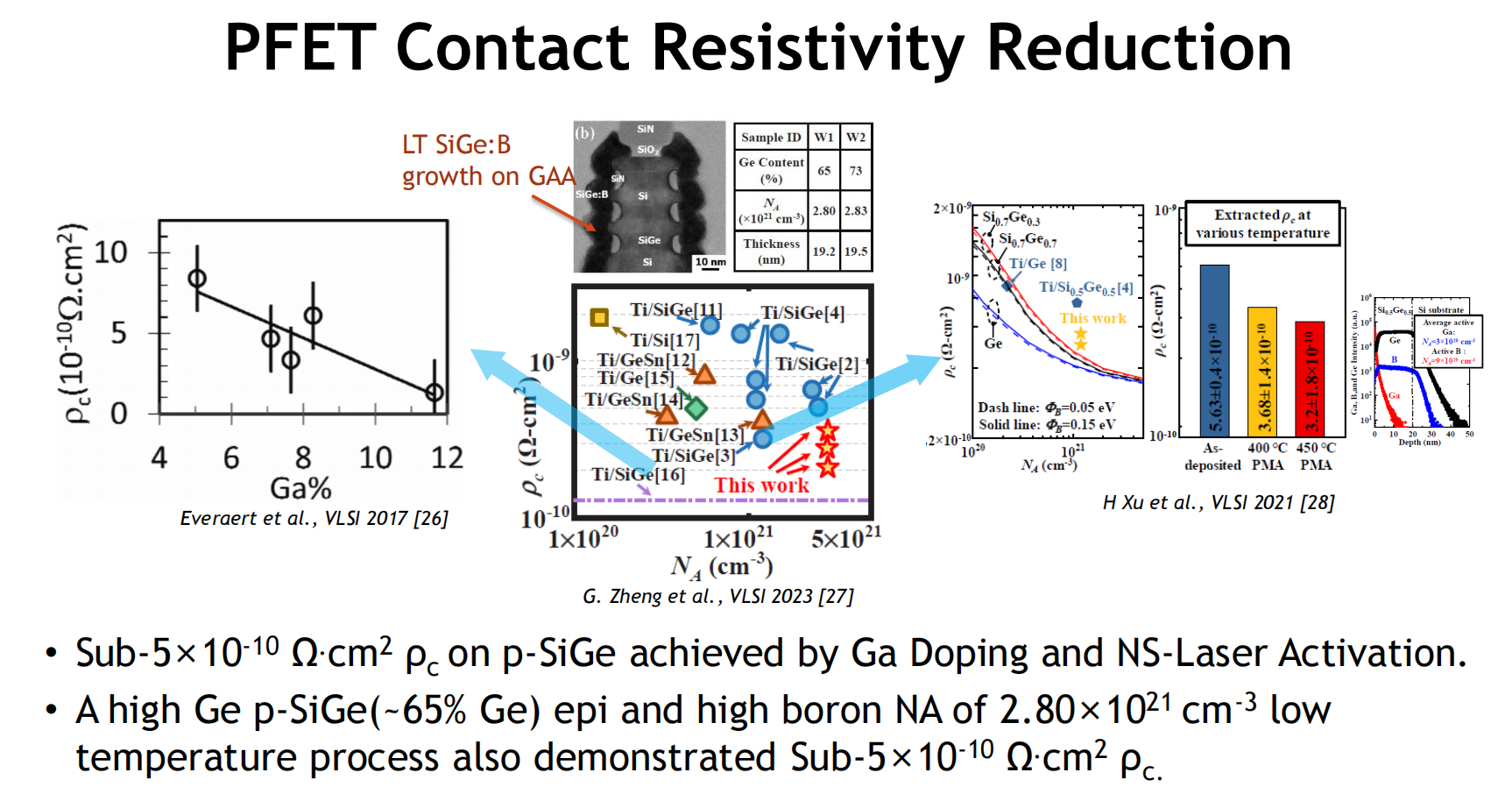

• 接触电阻下降:Sub-10⁻⁹ Ω·cm²时代

•对于PFET,采用高Ge p-SiGe外延+Ga掺杂+激光退火工艺,可实现<5×10⁻¹⁰ Ω·cm²的接触电阻水平。

•对于NFET,Ti基接触+毫秒级固相外延(SPE)或纳秒激光外延(LPE)成为主流路径。

漏电控制是一场多路径抑制战,结构、电场、材料三层协同,方可锁住每一毫瓦功耗窗口。

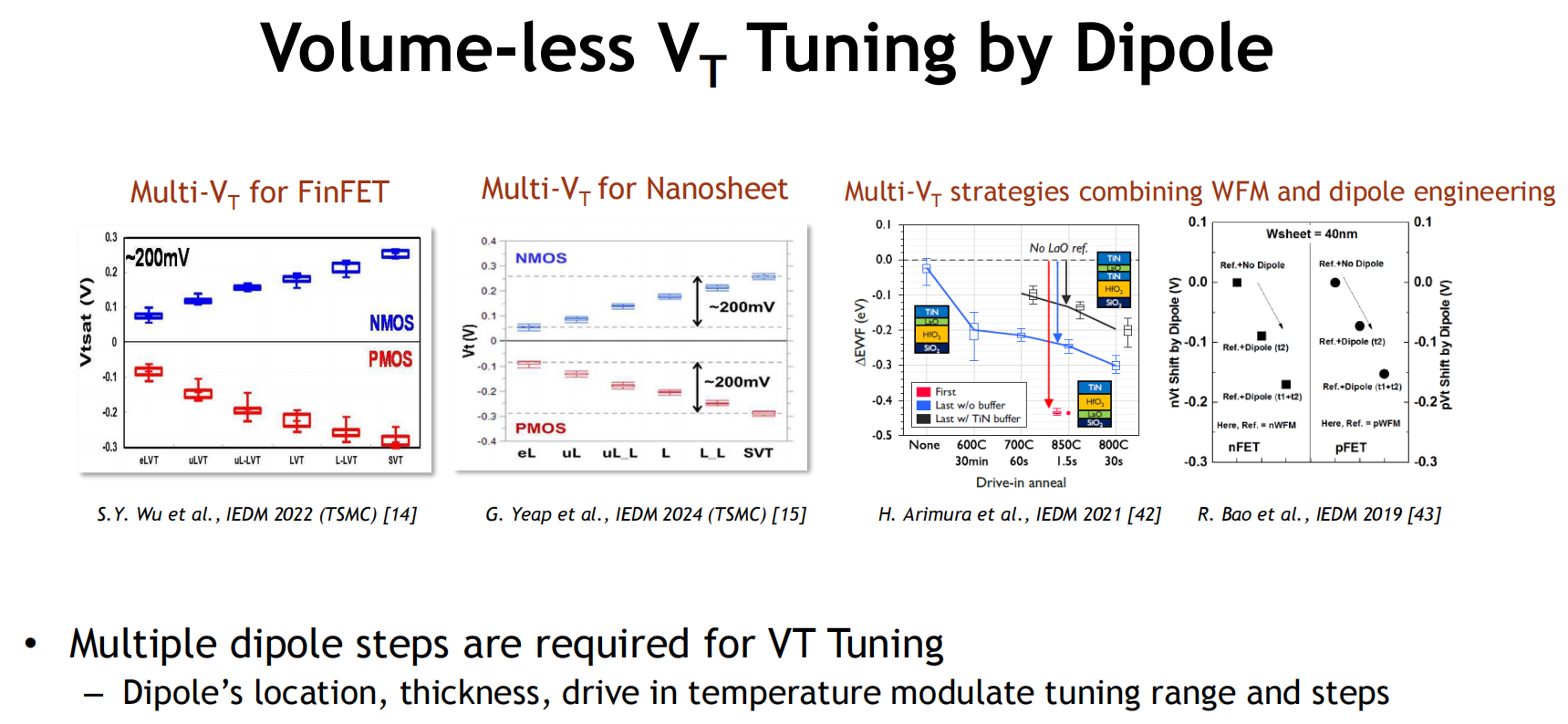

多VT设计:从厚度控制到无体积调控

极限尺寸下,传统基于金属厚度变化的VT调控方式已遭遇空间与变异的双重瓶颈。为适应GAA/Nanosheet结构的紧凑片宽,业界转向“无体积”VT调控(volume-less VT tuning),其核心手段包括:

·偶极工程(Dipole Engineering):通过在IL/High-k界面引入偶极层改变能带对齐,从而调控功函数。

·材料选择:利用如La₂O₃、Al₂O₃、TiO₂等材料诱导正负偶极,分别适用于PFET/NFET路径。

该策略不仅突破了厚度控制的热退火约束,更支持多级VT窗口精细调控,已被TSMC等厂商纳入主力GAA平台。

极限缩放时代,性能不是某一节点的属性,而是结构、电学、材料与设计“四维博弈”的结果。

四、工艺现实挑战与可制造性限制

在极限工艺节点下,性能与PPA的优化并非纯粹的技术能力问题,更是对制造变异、设计波动与热物理瓶颈的综合应对能力。先进逻辑制程的真正门槛,往往不在“能否设计”,而在“是否可量产”。

工艺变异:从统计到系统的双重挑战

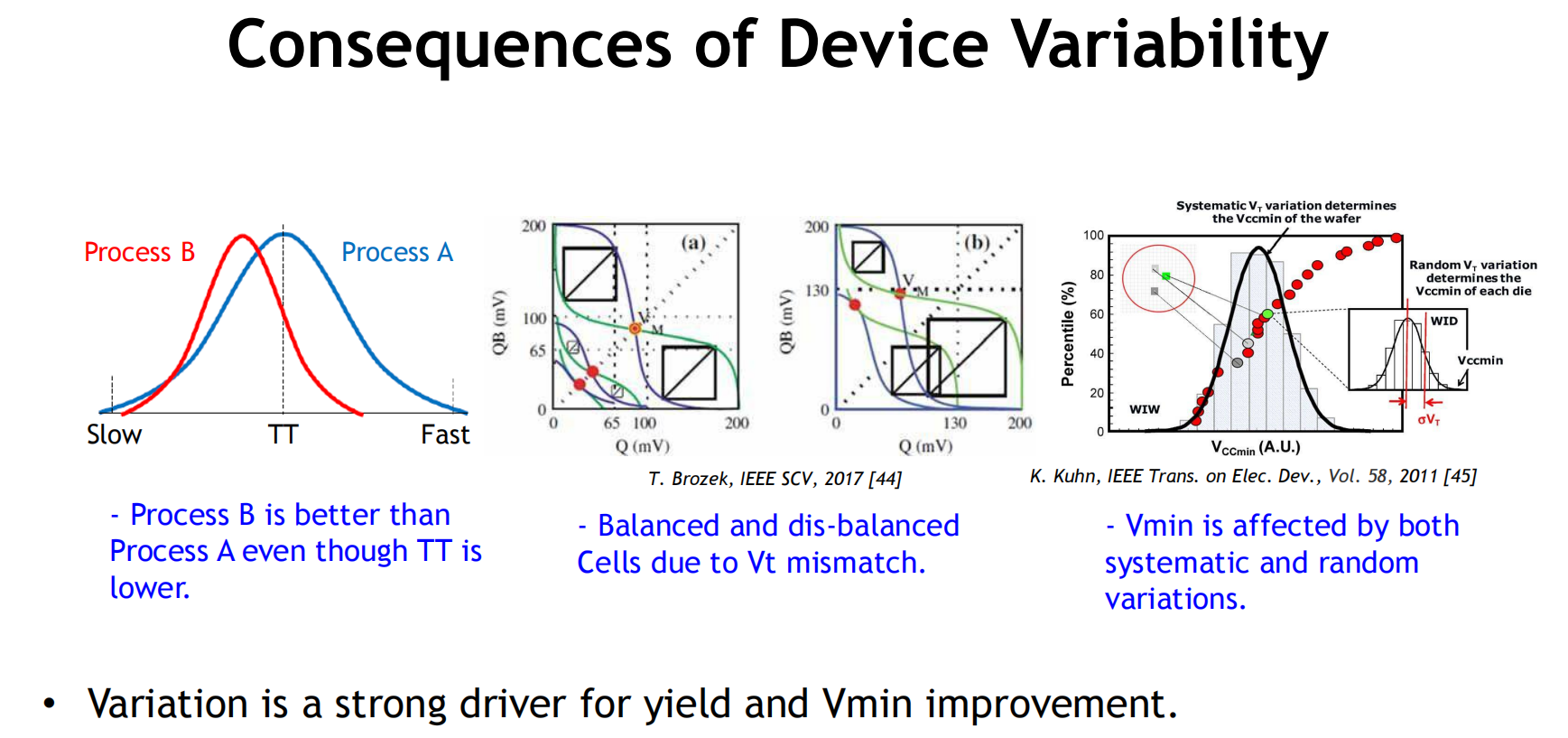

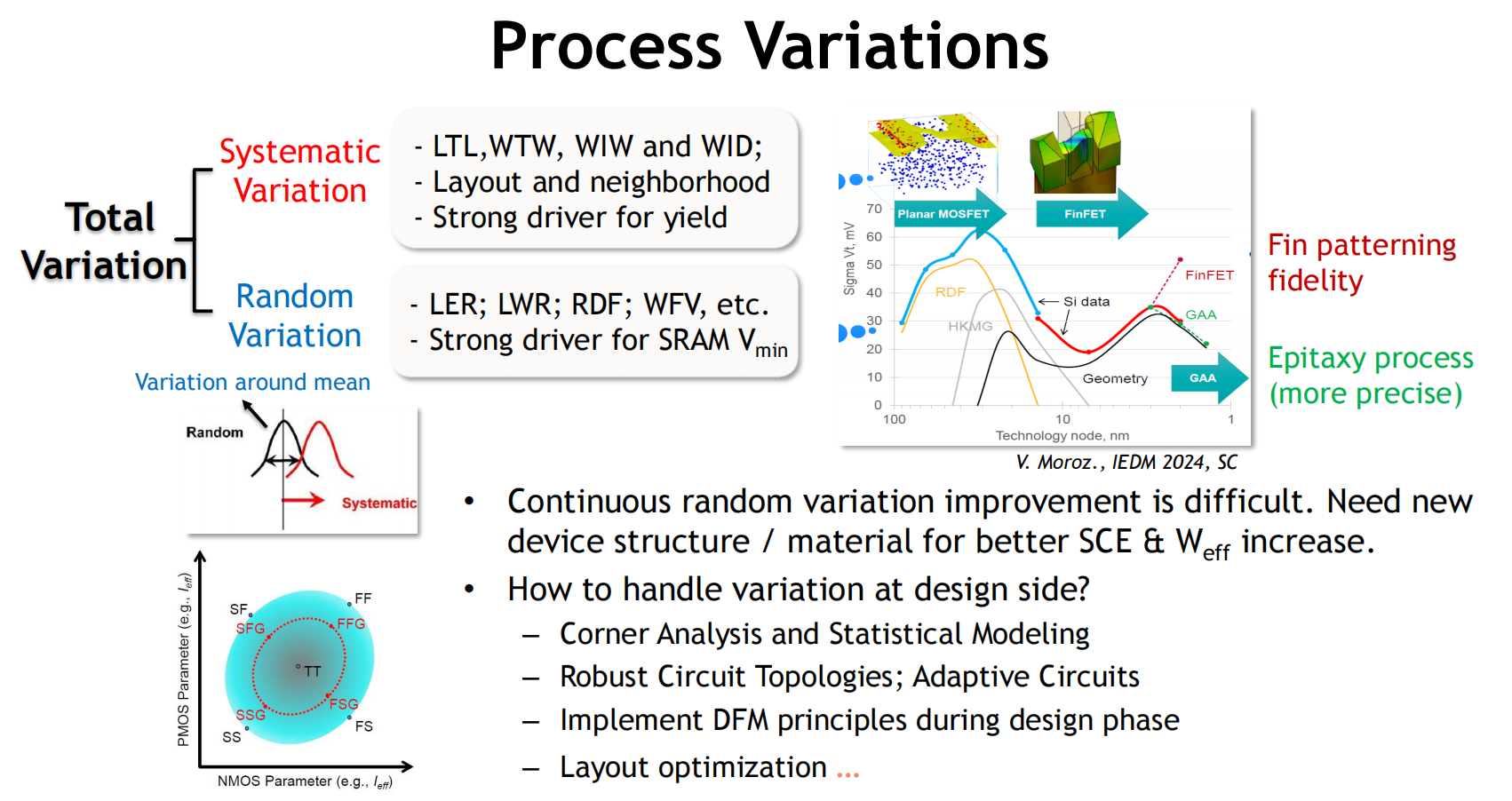

现代CMOS设计正面临前所未有的制造变异复杂性,主要分为:

·系统性变异:如晶圆间(WTW)、晶圆内(WIW)、布局相关(Layout-Dependent)等,会导致不同单元间Vt失配,直接影响Vmin与时序收敛。

·随机性变异:如线边粗糙(LER)、随机掺杂波动(RDF)、鳍宽波动(WFV)等,在SRAM等结构中尤为致命,成为Vmin控制的主因。

TSMC在IEDM展示数据显示:即使TT角(Typical-Typical)对齐,系统性变异仍可能导致不同工艺组合下的性能差异高达多个σ级别,严重制约设计预测性与良率窗口。

工艺变异正从统计偏差,演化为影响系统设计稳定性的决定性变量。

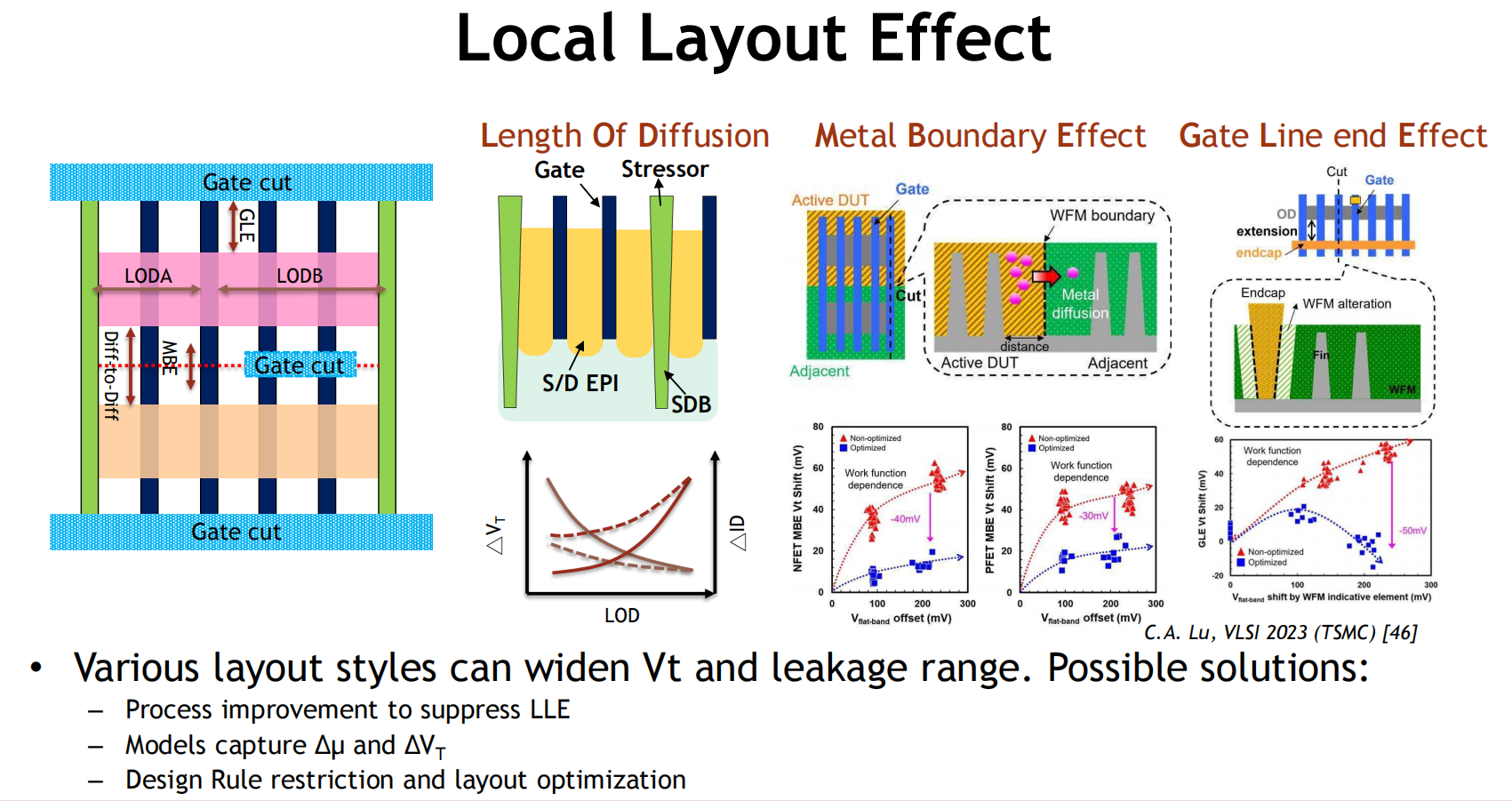

局部布局效应:VT偏移与泄漏扩散源

在先进节点中,Local Layout Effect(LLE)已成为影响器件一致性的主要非理想因素。主要包括:

·LOD(Length of Diffusion):扩散长度影响应变张力与VT;

·GLE/MBE(Gate Line-end/Metal Boundary Effect):金属终点或边界附近电场扭曲,导致迁移率波动;

·SDB带来的非对称接触排布:进一步拉大差异化。

解决方案需从三层协同入手:

·工艺侧压缩变异窗口;

·建模侧加入LLE捕捉参数;

·设计侧引入版图规则约束与优化模板。

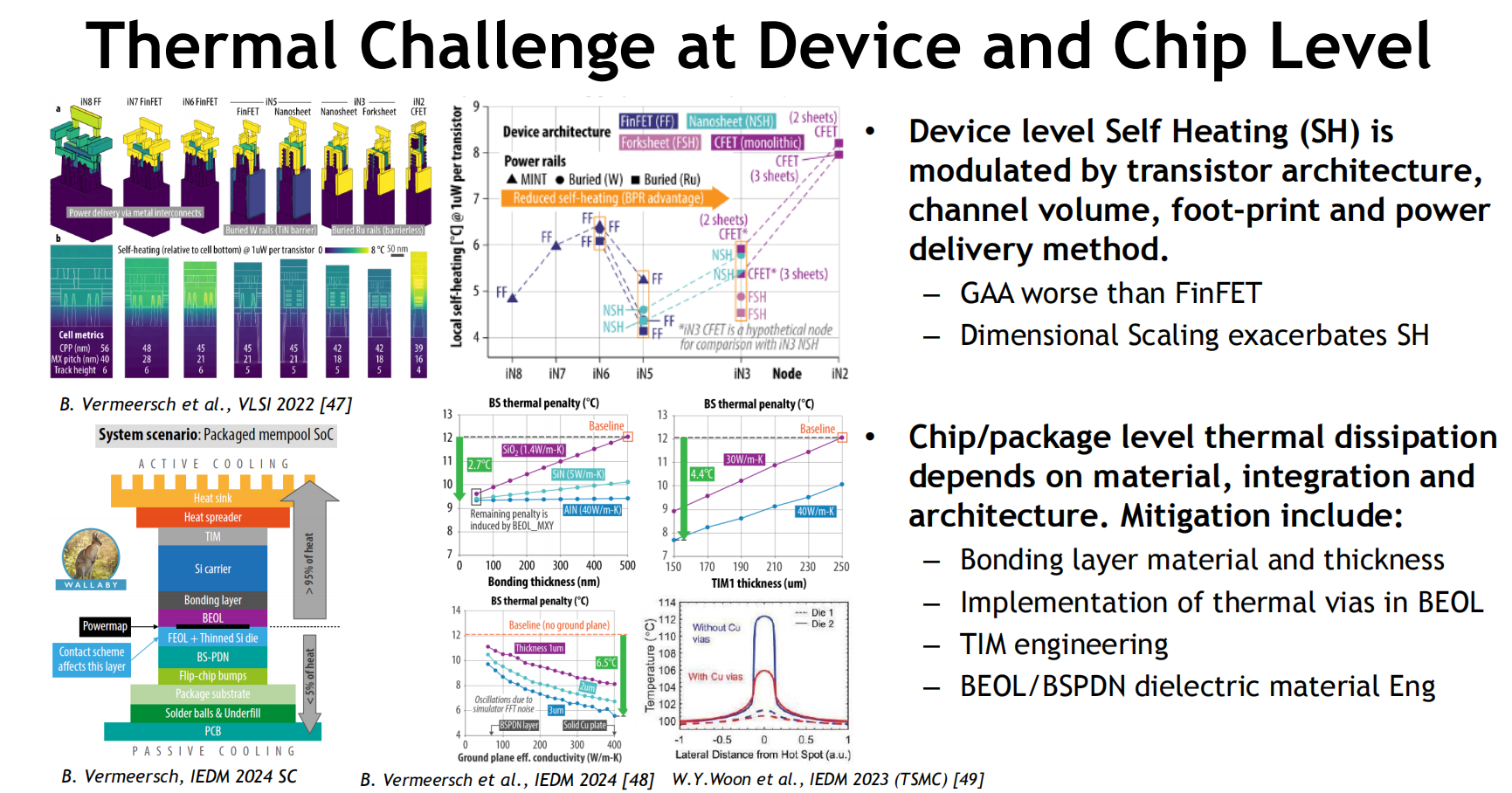

热挑战:从自加热到系统散热

极限尺寸下,单位面积功耗密度提升,自加热效应显著上升。TSMC研究指出:

·在相同功率密度下,GAA结构的自加热效应普遍高于FinFET,对载流子迁移率、VT稳定性产生长期影响;

·同时,芯片级热阻主要由封装热界面、BEOL材料、粘接层厚度与热通孔布局共同决定。

有效的热管理策略包括:

·引入低热阻TIM材料与热通道结构(Thermal Vias);

·优化背面金属堆叠与封装几何布局;

·在系统级采用热均衡调度算法与动态功耗管理。

可制造性提升路径:从EDA到架构协同

面对这些挑战,工艺-设计协同能力成为决定“先进工艺是否能量产”的关键因素。具体路径包括:

·在设计阶段引入Corner分析、Statistical Modeling、DFM规则集成;

·布局侧引导采用鲁棒电路拓扑结构与可变Vmin优化策略;

·从架构层预留工艺波动的冗余区间,提升系统容错性。

极限节点的良率,不再由晶圆厂决定,而是由“设计-工艺-架构”三方共同定义。

五、系统集成路径与STCO趋势

当晶体管缩放成本陡增、物理边界逼近,逻辑系统的竞争优势,正逐步从“器件制程”上移至“系统架构”。系统集成不再是封装团队的后处理,而是半导体竞争战略的核心组成。

Chiplet架构:打破SoC一体化瓶颈

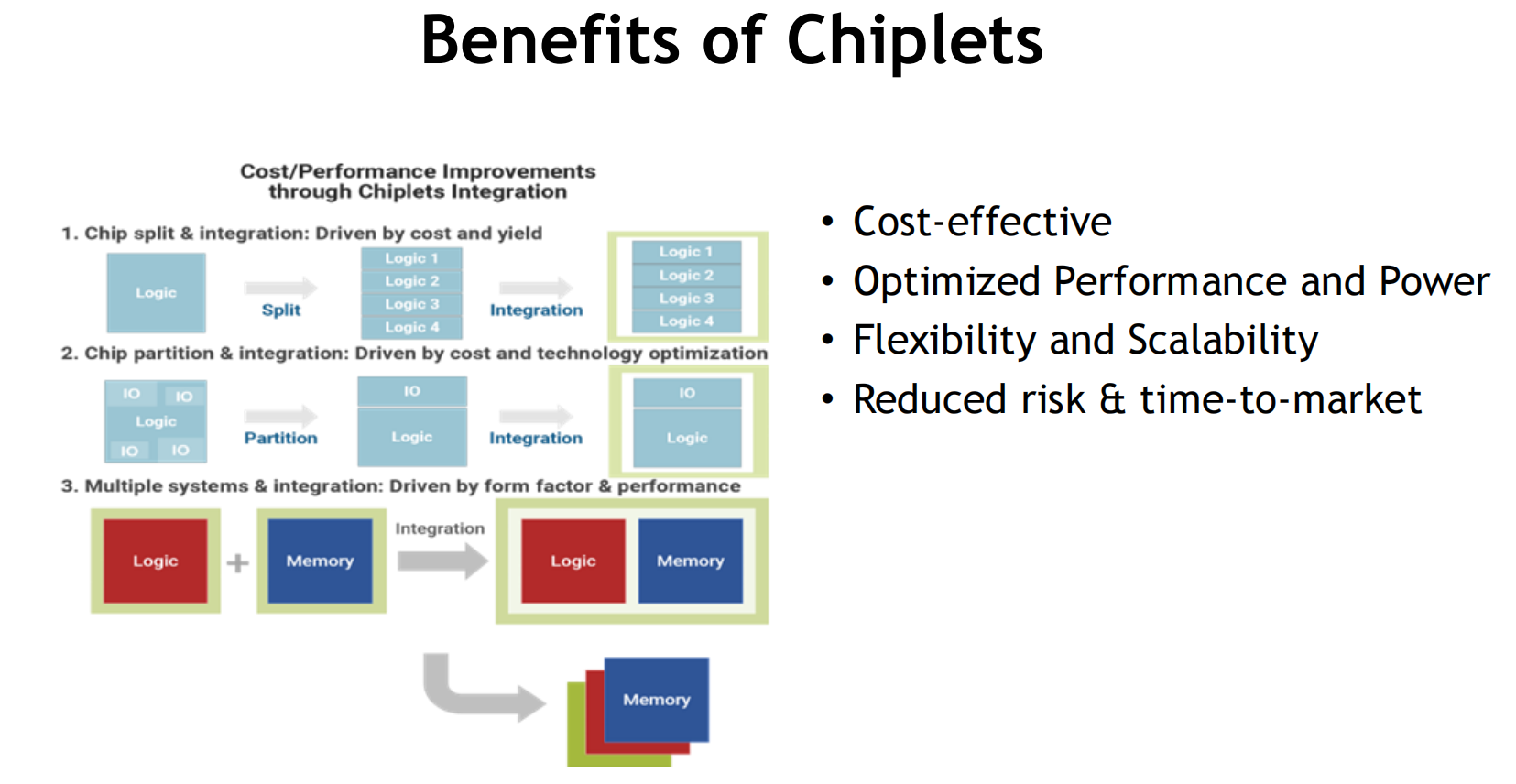

随着工艺代际推进,SoC设计面临PPA优化难度、IP整合复杂度与验证周期同步上升的问题。Chiplet(芯粒)架构应运而生,其核心理念是:

·将SoC分解为多个异构模块(逻辑、存储、I/O、AI加速等);

·各芯粒可采用不同节点、不同工艺平台独立优化;

·通过高密度互联重构为系统级解决方案。

TSMC指出,Chiplet具备成本优势、功耗/性能最优化、系统可扩展性强与开发风险可控等特性,正成为高性能计算(HPC)与数据中心芯片的主流路径。

从SoC到Chiplet,系统设计从“单芯片压榨极限”,转向“多芯片协同优化”。

高密度互联:解锁系统级集成能力

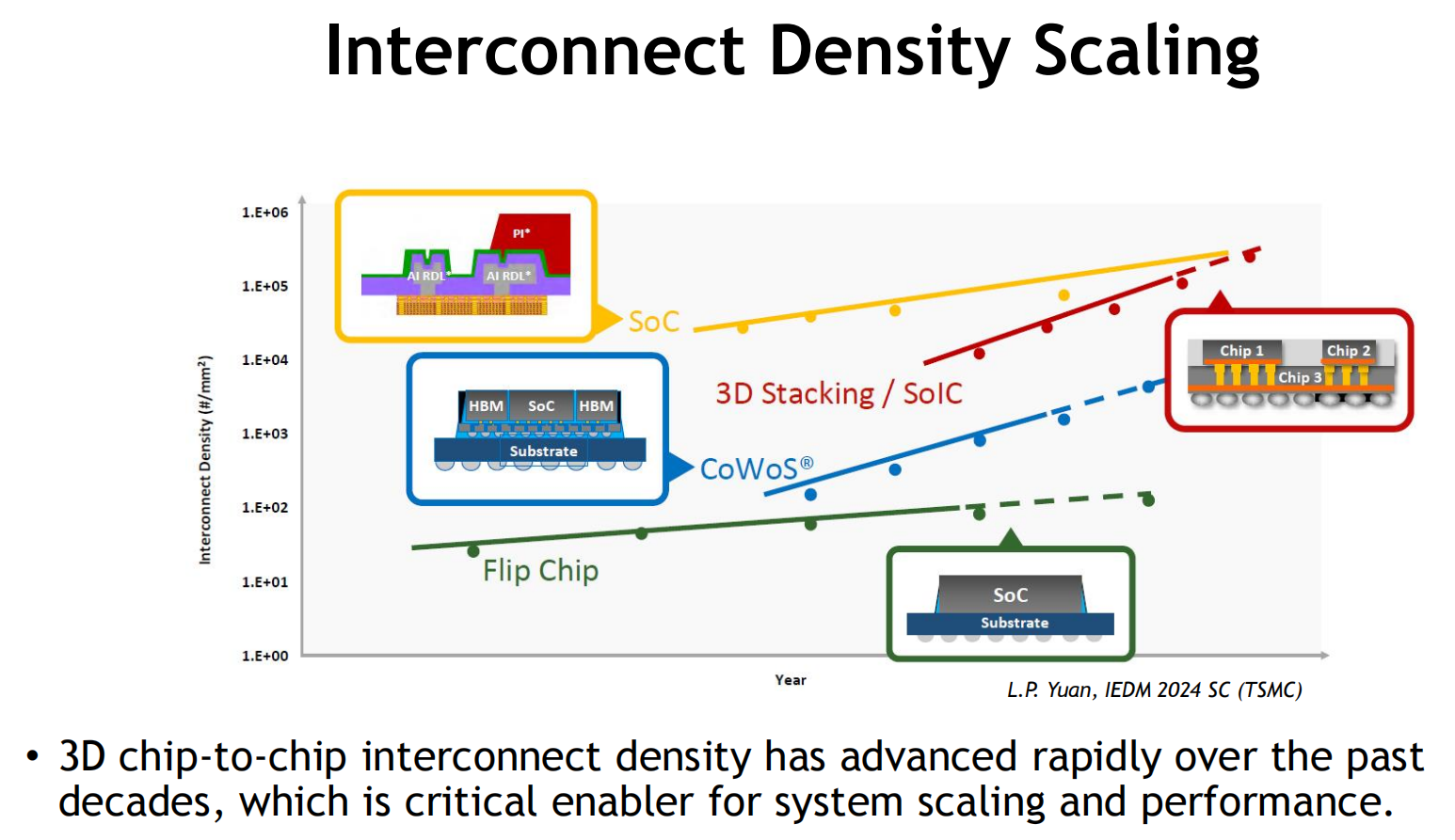

系统级封装的瓶颈在于芯粒之间的互联密度与延迟控制。为此,行业推动以下关键技术:

·2.5D/3D封装:如CoWoS、InFO、EMIB等,实现高带宽、低功耗芯粒互联;

·Hybrid Bonding / Direct Bonding:原子级接触方式,有效降低互联pitch与RC延迟;

·TSMC示例:最新系统封装方案可在单一封装内整合超过1万亿晶体管,等效于多个SoC级芯片同时协同运行。

封装工艺已不再只是“连接方式”,而是系统PPA优化链条中的第一性变量。

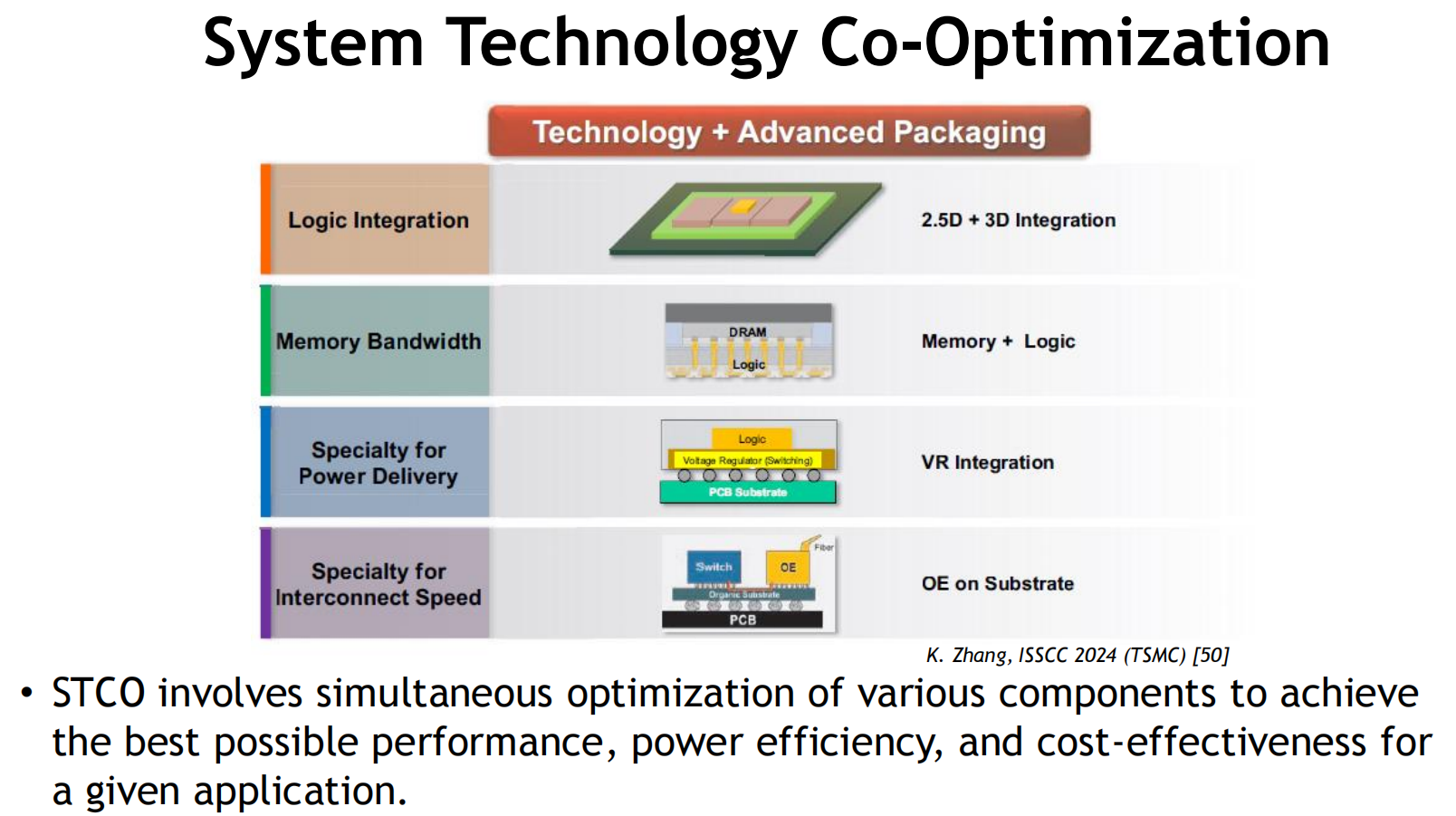

STCO:系统技术协同优化的路径重构

传统DTCO侧重于单元级设计与制程协同,而STCO(System Technology Co-Optimization)则将优化维度进一步扩展至:

·应用算法与芯片架构的联合设计;

·芯粒功能划分与异构协同的接口定义;

·封装/供电/热管理/互联等系统级物理实现共优化。

在STCO范式下,芯片设计不再从“工艺节点”出发,而是从“系统目标”反推最优实现路径。例如:

·AI芯片中,将运算阵列置于先进节点,而控制逻辑、SRAM留在成熟节点;

·高速SerDes模块使用高fT工艺,而低速管理模块则以低功耗工艺实现。

先进工艺决定上限,STCO决定极限是否真正被用到。

六、总结与展望

回顾CMOS技术演进路径,逻辑缩放从未止步,但其推动力与突破方式早已今非昔比。从Dennard时代的线性缩放,到后摩尔时代的结构重构与系统协同,半导体技术的每一次跃迁,都是产业工程、科学创新与协同思维的交汇结果。

结构层面,从FinFET到GAA,再到CFET的接力突破,让密度得以持续增长;设计维度,FinFlex、NanoFlex与多VT技术将工艺优势交还设计者;材料领域,从eSiGe通道、极限EOT堆叠,到低接触电阻工程,每一个工艺细节都成为性能和能效的平衡器。

但同时,变异、热管理、互联与制造复杂性已成为先进制程绕不开的现实门槛。在逻辑缩放接近极限之际,系统思维开始主导竞争格局:

·DTCO定义芯片层级的极限使用率

·STCO定义系统层级的整体性能边界

Chiplet与高密度封装的普及,使“系统级摩尔定律”成为行业共识:每两年翻倍的,不再是晶体管数量,而是“系统集成的计算密度与能效能力”。

未来的CMOS演进路径,不会是单一维度的延伸,而将是一条融合材料、结构、设计、封装与架构的多元曲线。正如TSMC在报告中所强调:技术突破不再孤立发生,而是依赖“协同创新”与“系统复合优化”能力的全面崛起。

CMOS缩放仍在继续,只是赛道已变:从纳米线宽的极限竞赛,转向跨层协同的系统进化。

来源:《半导体产业报告》

免责申明:文章版权归原作者所有,如您(单位或个人)认为内容有侵权嫌疑,敬请立即通知我们,我们将第一时间予以更改或删除。