玻璃基板:先进封装的下一站?

过去十年,先进封装技术一路高歌,成为撑起摩尔定律的关键补位手段。但当芯片封装愈加复杂、系统互连密度暴增、AI 算力需求翻倍时,材料,成了决定系统性能上限的新变量。

我们已经看到了硅中介层的极限,看到了有机材料的妥协。产业开始回头去看一个被忽视的老朋友——玻璃。

玻璃基板,正在从“小众技术”走向产业主舞台,被寄望于重构 Chiplet 封装、高带宽互连、光电集成的基础平台。英特尔、Corning、Absolics、DNP 等重量级玩家纷纷下注。

这一次,它不是概念,而是真正迈入工程验证和商业化前夜。

一、当封装走到拐点,材料就成了变量

封装不再是“后工艺”,而是芯片系统性能的第一战场。

尤其是 AI 的爆发,对 GPU-HBM 的带宽和能效提出前所未有的要求。高带宽内存继续进化,但连接 GPU 与 HBM 的封装互连,已成为系统性能瓶颈。

TSMC CoWoS、Intel EMIB 虽然代表了当前主流的硅中介层路径,但它们也暴露出高成本、封装尺寸限制、可靠性不足等问题。

于是,玻璃基板以一种近乎“折中”的理想状态进入视野:

比硅便宜,比有机材料稳定,比封装中介层更可扩展。

如果它真的能成立,那么玻璃不仅是材料选择,更是封装体系的根本性重构。

二、为什么是玻璃?三大逻辑撑起材料跃迁

从材料科学的角度来看,玻璃确实具备改变游戏规则的底层能力:

1)性能维度:电性能更优

·高电阻率、低介电损耗,TGV(Through-Glass Via)插入损耗比 TSV 低 1–2 dB

·支持超高速信号传输:<2 ps 抖动、70 Gbps数据速率

·更小串扰:介电常数更低,适合高密度封装

2)制造维度:结构化能力强 + 面板级扩展性

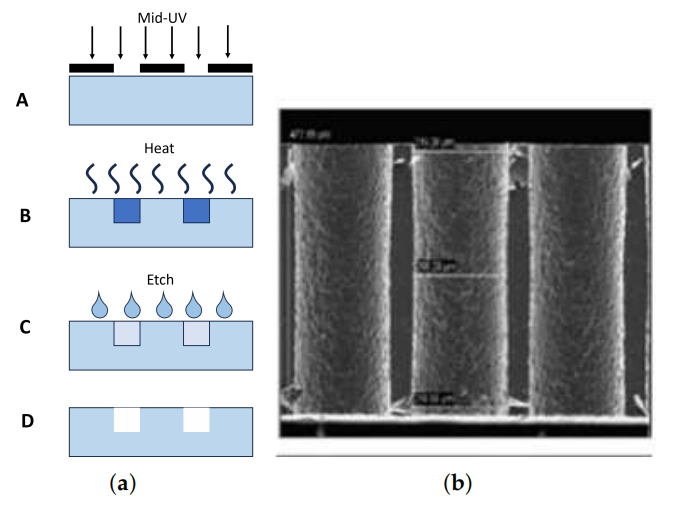

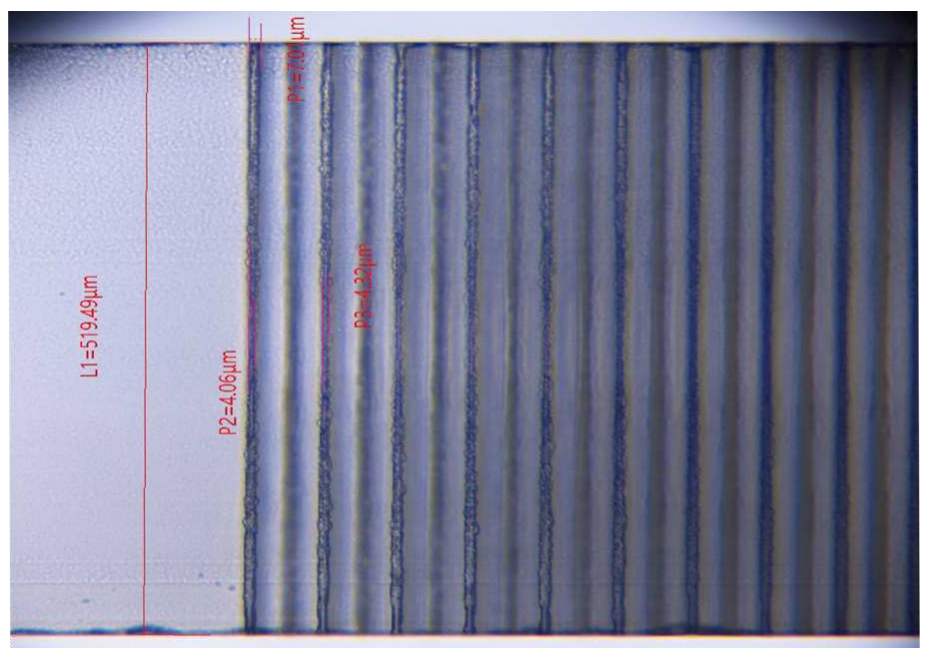

·可通过激光、湿法、等离子体蚀刻等方法制备高深宽比 TGV

·支持 500mm 以上大面板加工,适合未来“系统级封装”(System on Panel)路线

·优异的尺寸稳定性,适合高精度对位

3)系统整合维度:封装、嵌入、光电集成一体化

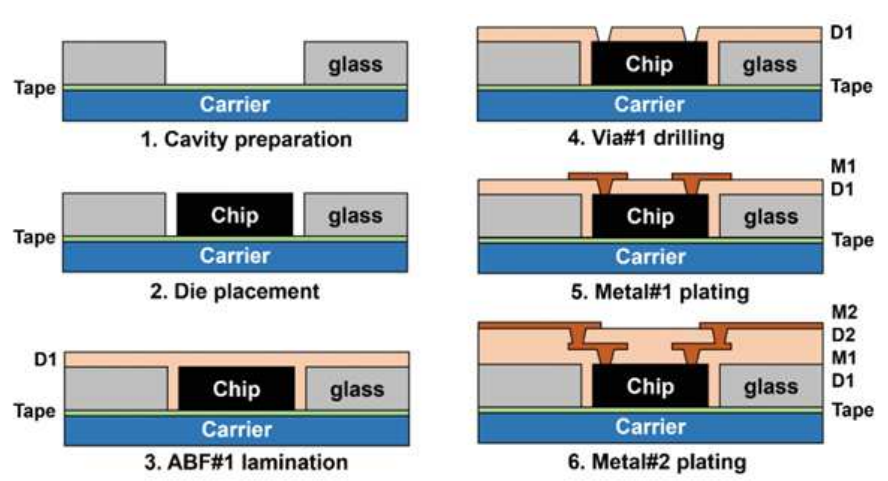

·可直接嵌入芯片,构建 GPE(Glass Panel Embedding)架构

·集成光波导、透镜、天线等光电器件,适合毫米波、光通信、AIP 等应用场景

三、不是空谈,是真正走到商业化前夜

这轮玻璃基板的热潮不是喊口号,而是真实的工程落地:

➤ 全球企业纷纷下注:

·Intel:展示三层 build-up 的玻璃基板样品,面向 AI 加速器封装

·Absolics:在美建厂,目标 2025 实现玻璃基板小批量生产

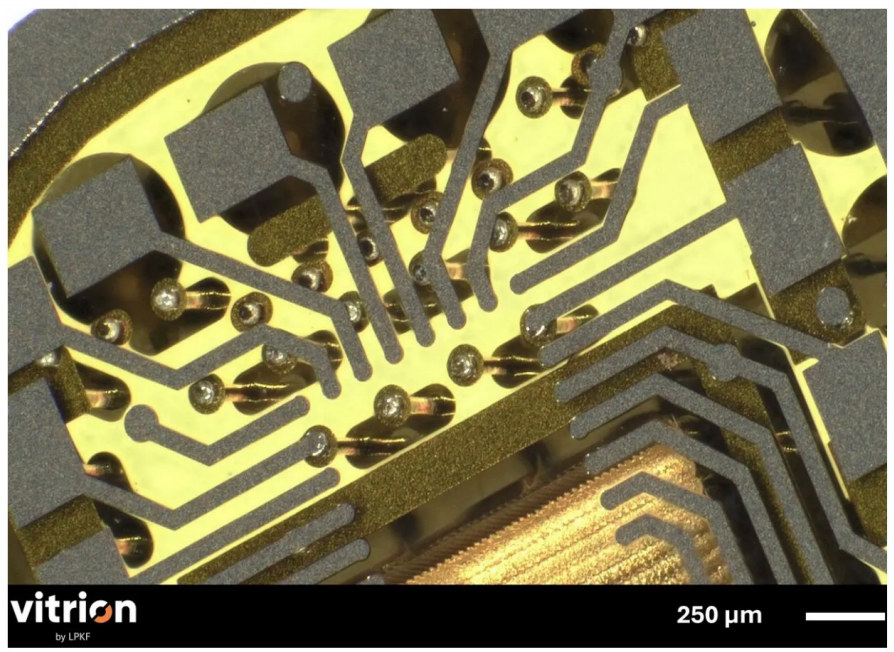

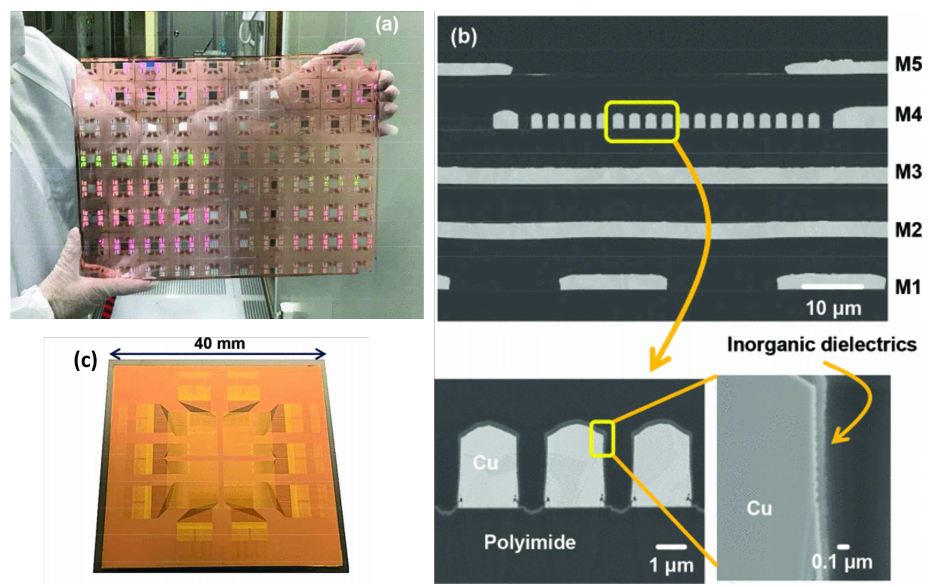

·DNP:实现 2μm RDL + 高密度互连的玻璃中介层

·3DGS:将光波导与 TGV、RDL 一体集成,打造光电封装平台

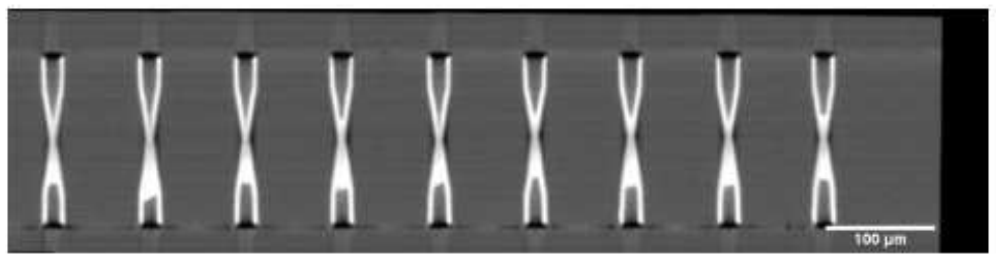

·Vitrion、Xiamen Sky-semi、Planoptik:实现 >10:1 的高深宽比 TGV,加工尺寸达 500mm 以上

➤ 架构层面,GPE 成为突破口:

·芯片先嵌入玻璃腔体,RDL 后封装

·IO pitch 可缩小至<20μm,die-to-die 间距压缩至 <100μm

·不依赖 TSV,真正实现 Chiplet 高密度集成与光电异构融合

四、技术好,不代表能量产——三大挑战仍在眼前

即便玻璃基板“听起来完美”,落地依旧充满现实问题:

1)制造良率:依然是首要“卡脖子点”

·激光钻孔 + 湿法蚀刻 TGV 制程复杂

·电镀一致性难以保证,大尺寸面板中心和边缘镀层厚度不同

·TGV 金属化过程易出现空洞、脱层、微裂纹

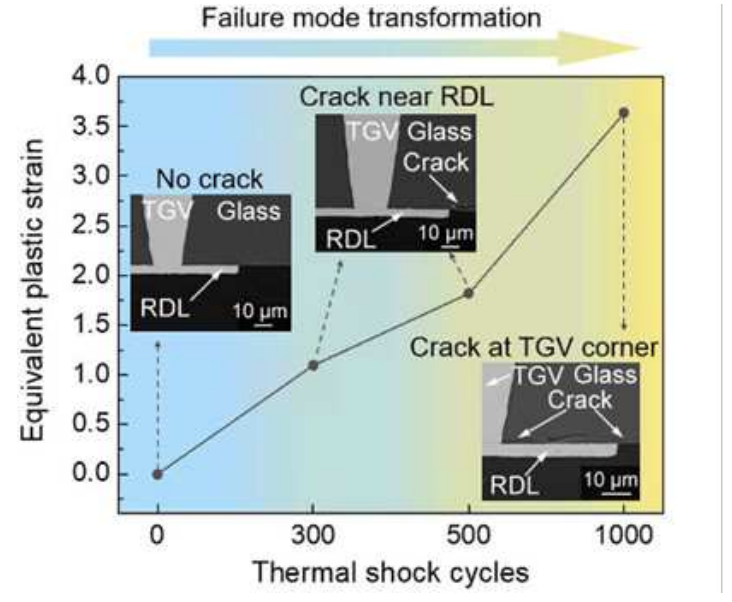

2)可靠性挑战:CTE(热膨胀系数)失配依然危险

·铜与玻璃膨胀系数差异大,热循环容易导致应力集中

·BGA 焊球疲劳失效几率上升,尤其在低 CTE 玻璃下更明显

3)系统集成与EDA支持:设计工具链尚不成熟

·光波导、毫米波天线、滤波器在玻璃上的布线规则需重构

·EDA 工具对玻璃介质模型的支持不完善

·封装热管理仍需新架构(热 vias、金属散热器、开窗设计)

五、这是一场材料路线的豪赌,也可能是一次历史机遇

玻璃基板并不是短期“降维打击”的新贵,它是半导体封装在进入 Chiplet 时代、系统集成时代、光电融合时代后的必然探索。

它不是取代硅,而是:

成为 Chiplet 互连 + 光电混合 + 高频通讯 + 热分区控制的最优底座之一。

如果你今天在做:

·HPC / AI 封装架构

·高速信号与光电互连设计

·系统级封装(SoW、SoP)

那你,不能不关注玻璃基板的进展。

写在最后

材料跃迁,永远不是一场成本优化的算术题。

它往往意味着整条设计链、工艺链、供应链都要重构一次,并催生出一整代新的架构、工具与玩家。

而每一次这样的大迁移,都是技术力量重新洗牌的机会。

来源:《半导体产业报告》

免责申明:文章版权归原作者所有,如您(单位或个人)认为内容有侵权嫌疑,敬请立即通知我们,我们将第一时间予以更改或删除。