300nm混合键合:先进封装的下一道分水岭

混合键合不是“附属技术”,而是先进封装走向极限的主力路线。

先进封装的发展,已不再是“拼凑工艺”的简单组合游戏。

当后摩尔时代呼唤更高密度、更低功耗的异构集成方案时,传统的微凸点(μ-bump)技术显得捉襟见肘。而 Wafer-to-Wafer(W2W)混合键合,凭借其“无需焊料、极低pitch、高精度对准”的天然优势,正一步步成为先进封装的基石。

在这场“越走越细”的竞赛中,imec 成功将混合键合的互连间距(pitch)压缩至 300nm,不仅刷新了业内纪录,更揭示了一个事实:

混合键合,不再是趋势,而是现实。

🧪 从 400nm 到 300nm:每一步都是挑战

在此前的研究中,imec 已经实现了 400nm pitch 的可靠混合键合。然而,从 400nm 向 300nm 演进,绝非“线性缩小”那么简单,而是牵一发而动全身的系统工程。

为了实现更小的pad pitch,团队主要做了三方面的突破:

1. 关键尺寸压缩

· Hybrid pad 最小CD压缩到 100nm

·最小pitch达到 200nm

·引入 dummy pad 以保证铜密度和形貌连续性

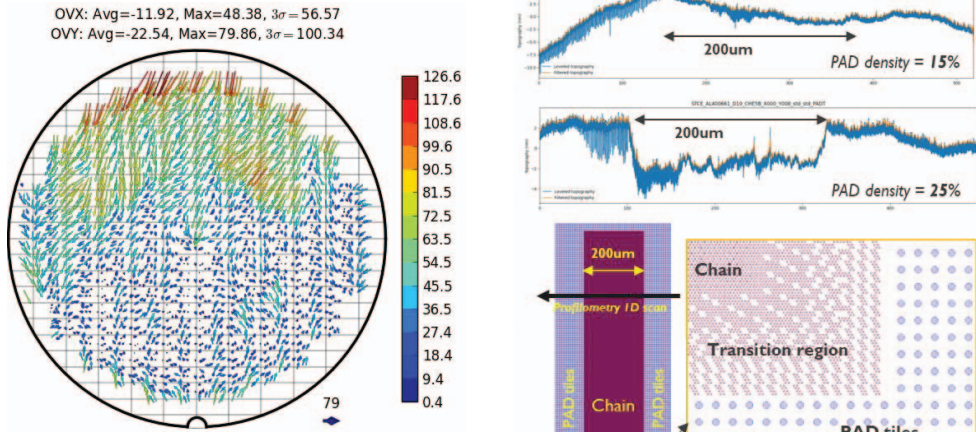

2. 形貌控制与叠合精度

·通过 六边形排布 + 密度渐变 设计,控制pad区域与空白区域的应力与平整度

·要在300nm pitch上保证电连接,overlay偏差必须控制在75nm以内

3. 工艺堆栈优化

·Dielectric stack 采用 SiCN/SiO₂/SiCN 三明治结构

·为降低 aspect ratio,整体pad深度从350nm压缩至250nm

·多道 CMP 工艺控制 pad recess 在 2~3nm 之间,保证平坦性

这一系列操作,不是“微调”,而是对先进制造极限的一次实质性试探。

🧩 电性验证:能连接还要能跑得动

实验不是为了“贴片展示”,而是为真实产品铺路。

为了验证工艺稳定性,研究中使用了 Kelvin结构 与 Daisy Chain结构 进行电性测试:

✅ Kelvin测试结果:

·400~500nm pitch,良率接近 100%

·350nm 仍能维持 高良率

·300nm 时,若pad密度控制在 20%,良率仍可达 70~80%

“铜凸起”(Cu bulge-out)效应是关键机制,它能弥补轻微overlay误差,实现连接闭合。

但如果上下pad尺寸相等且铜密度过高(25%),容易在bond界面形成空洞,造成良率下降。

✅ Daisy Chain测试结果:

·300nm pitch 的大规模链路结构,仍保持高良率

·相比Kelvin结构,Daisy Chain对空洞更具容忍性

这一部分验证了一个核心认知:

“连接”这件事,不仅关乎尺寸,还关乎形貌、密度、应力场之间的整体协同。

📌 形貌、应力、密度:隐藏在pitch背后的三体问题

如果只看论文中“300nm、100nm、75nm”的数字,会觉得这像是一场极限运动。

但 imec 真正突破的,其实是隐藏在背后的“三体问题”:

🔹 第一体:形貌的可控性

·表面粗糙度 ≠ 平整度

·Recess控制在2~3nm,还要应对由pad密度差异造成的“局部台阶”

·没有dummy pad的区域,抛光难以均匀

🔹 第二体:应力场的分布

·在晶圆边缘、密度突变区域,容易形成不均应力

·如果应力场在bonding前未解耦,将在叠合过程中“放大问题”

🔹 第三体:铜密度的动态变化

·高密度带来“易连接”,但也带来“电介质腐蚀”和“界面空洞”

·设计铜密度从15%、20%、25%逐级测试,找到最优窗口

这些变量,不是各自独立,而是彼此牵制,形成高度耦合系统。

真正的挑战,是在工艺窗口极窄的情况下,确保每一片晶圆、每一个pad都能连接、导通、可靠。

🧭 下一步:从 300nm 到 200nm,物理极限在哪里?

文章结尾处,imec 明确提出:

目标是继续缩小 hybrid pad pitch,下一阶段将开发更小尺寸的 test vehicle。

但问题是:

·再缩,就逼近图形化能力极限(litho + etch)

·再缩,就面临热预算与材料界限

·再缩,连接精度必须进入 <50nm overlay 级别

这不再是“封装问题”,而是光刻、CMP、材料工程等多个学科交叉的结果。

所以我说:

混合键合已经不是“封装的边缘工艺”,它正在吞噬前端的定义。

来源:《半导体产业报告》

免责申明:文章版权归原作者所有,如您(单位或个人)认为内容有侵权嫌疑,敬请立即通知我们,我们将第一时间予以更改或删除。