晶圆级混合键合中的芯片拉伸现象解析

引言

芯片到晶圆(D2W)混合键合技术已成为构建下一代半导体器件的关键技术,这些器件要求高带宽、优异性能和最小功耗。随着产业向更复杂的3D集成方案发展,理解和控制叠层误差对于实现高电气良率和最佳封装性能变得极为重要。这一过程中最显著的挑战之一是芯片拉伸现象,会降低器件良率并增加电阻。Applied Materials和Back End Semiconductor Industries的研究人员开发了复杂的物理模型来理解和缓解这一现象,为从事D2W键合工艺优化的工艺工程师和设备设计师提供了宝贵见解[1]。

D2W键合工艺及其挑战

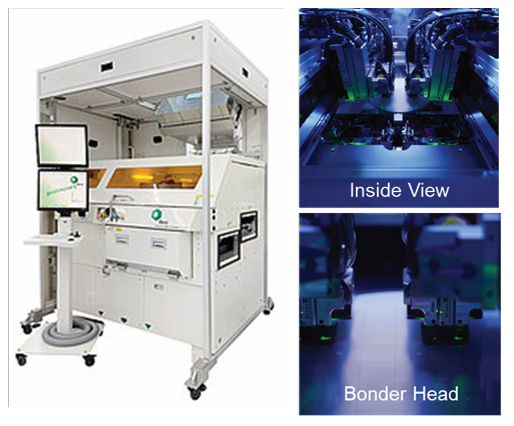

芯片到晶圆键合序列涉及几个精确协调的步骤,这些步骤必须无缝配合。工艺从使用真空压力将芯片吸附到键合喷嘴开始,随后小心地将芯片接触到衬底晶圆上。初始接触后,根据可编程延迟释放固定芯片的真空,最后喷嘴回缩完成操作。虽然这个序列看起来简单明了,但控制每个步骤的物理机制却相当复杂,特别是在处理因上游工艺而表现出初始翘曲的芯片时。

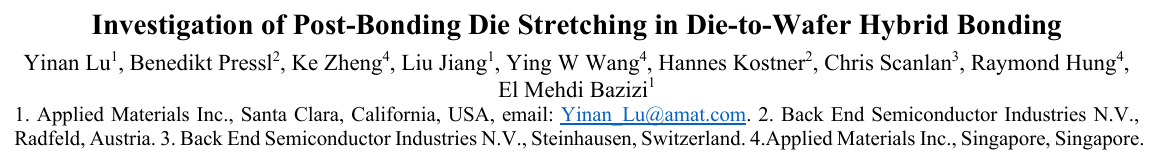

图1:Besi Datacon 8800 CHAMEO键合设备。

图2:D2W键合工艺的四个关键阶段:芯片吸附、接触、真空释放和喷嘴回缩。

与技术文献中已被广泛记录的晶圆到晶圆键合不同,芯片到晶圆键合由于芯片尺寸较小以及可能发生的众多工艺变化而呈现出独特挑战。较小的尺寸意味着边缘效应变得更加明显,键合前沿传播的动力学与大尺寸晶圆键合场景有显著差异。这需要一个专门的仿真框架,能够捕捉芯片在各种条件下如何键合到衬底的细微力学特性。

基于物理的建模方法

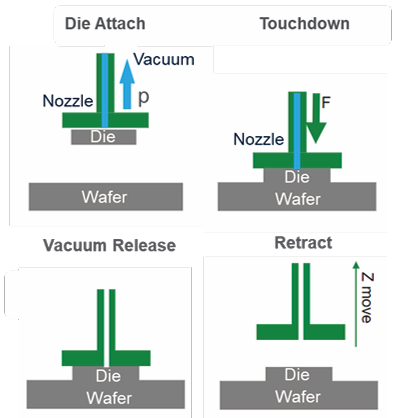

为了理解和预测芯片拉伸行为,研究人员开发了综合性的物理模型,该模型包含多个相互作用的现象。仿真框架包括键合工具几何形状的详细表示、具有初始翘曲轮廓的芯片以及衬底。模型的一个特别重要方面是如何处理键合的启动和传播。当真空吸附的芯片接近衬底时,芯片中心通常首先接触。这个初始接触点触发了由键合界面沿线的粘附力驱动的一系列事件。

图3:(a)显示了完整的仿真模型架构,包括键合工具、基座、芯片和衬底,而(b)展示了粘附压力和空气阻力如何随芯片-衬底间隙距离变化。

粘附力将芯片向下拉向衬底,导致接触前沿从中心向芯片边缘传播。为了准确模拟这种行为,模型采用了改进的Lennard-Jones势来表示作为芯片与衬底间隙函数的粘附力。同时,计算流体动力学(CFD)仿真预测了当空气从变窄的间隙中被挤出时阻碍芯片运动的空气阻力。这种空气阻力在控制键合前沿传播速度方面发挥了关键作用,最终影响芯片拉伸的幅度。

芯片的初始翘曲通过在面向衬底的芯片表面引入拉伸或压缩应力层来纳入模型。拉伸应力层诱导凸形翘曲,而压缩层则产生凹形翘曲。这些不同的翘曲轮廓显著影响键合过程的展开方式以及最终的芯片拉伸模式。

键合前沿传播动力学

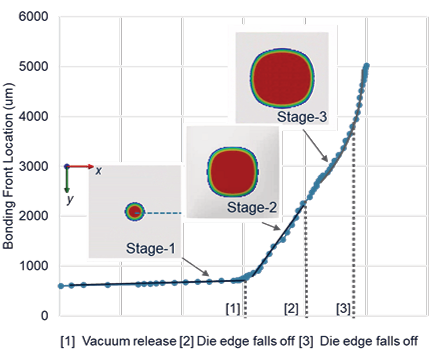

键合过程可分为三个不同阶段,每个阶段的特点是不同的力学行为和传播速度。在第一阶段,即接触后但真空释放前,键合前沿从中心向边缘缓慢传播。在此阶段,大部分芯片仍被真空压力吸附在键合喷嘴上,只有靠近中心的小区域与衬底接触。键合前沿在这个初始阶段通常只前进几百微米。

图4:键合前沿传播的三个阶段,实线显示了与实验数据点的曲线拟合,说明了真空释放后键合速度如何显著变化。

第二阶段始于真空开始释放,允许芯片有更多自由度来顺应衬底。这一阶段的特点是键合前沿传播的显著加速。真空吸附力的减少使粘附力能够更快速地将芯片拉向衬底,键合前沿的前进速度比第一阶段快得多。最后,在第三阶段,残余真空压力无法再将芯片固定在键合喷嘴上,芯片被快速拉下,在整个表面上完成键合。理解这三个阶段非常重要,因为芯片拉伸主要发生在早期阶段,当时中心区域在仍被真空吸附时被拉伸。

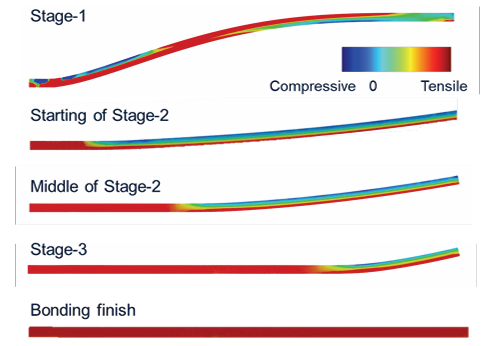

图5:应力分布如何在键合过程中演变,蓝色代表压缩应力,红色显示导致永久芯片拉伸的高度拉伸的拉应力区域。

芯片在这些阶段内的应力分布揭示了拉伸发生的原因。在第一阶段接触后立即,芯片的中间区域经历高拉应力,因为在边缘仍被真空吸附的同时,中间被粘附力向下拉。随着键合前沿向外传播,这些被拉伸的材料被永久键合到衬底上,锁定了拉伸变形。拉伸的幅度关键取决于真空释放的速度以及在整个芯片接触之前键合前沿能够传播的速度。

验证与工艺优化

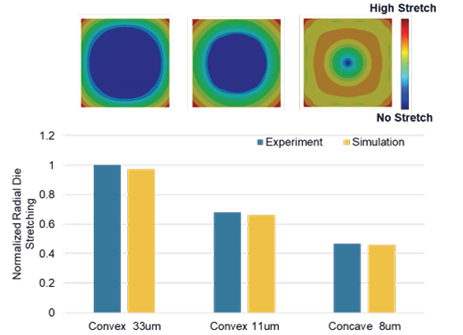

该仿真模型已通过使用实际键合设备处理代表存储器应用的10毫米方形芯片的实验测量进行了严格验证。验证研究检查了三种不同的初始翘曲轮廓:33微米翘曲的凸形、11微米翘曲的凸形和8微米翘曲的凹形。仿真结果在所有三种翘曲条件下都与实验芯片拉伸测量显示出优异的一致性,证实了模型的准确性和预测能力。

图6:实验测量(柱状图显示)与三种不同初始芯片翘曲条件的仿真预测进行比较,展示了模型与实际情况之间的优异一致性。

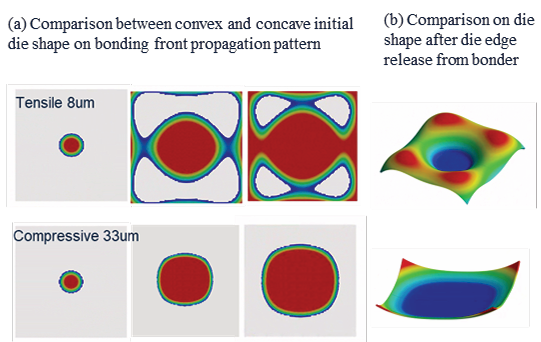

初始芯片翘曲对键合行为的影响不仅仅体现在最终拉伸的幅度上。具有拉伸应力的芯片在真空开始释放后在边缘表现出向下倾斜,启动了从边缘向中心传播的额外键合前沿。这创造了一个更复杂的键合模式,前沿同时从中心和边缘向前推进。相比之下,具有压缩应力的芯片在键合过程中显示出向上倾斜的边缘,导致更长的整体键合时间和不同的拉伸模式。

图7:(a)显示凸形芯片形状如何从中心和边缘创建键合前沿,而(b)展示了不同翘曲条件下真空释放后的3D芯片变形。

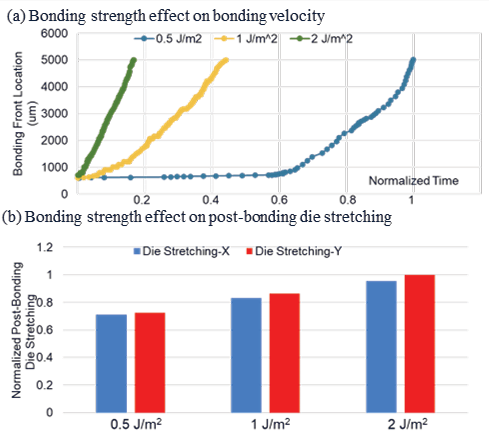

键合能量由表面处理如等离子体活化控制,也显著影响键合速度和最终芯片拉伸。没有活化时,硅-硅键合能量相对较低,但等离子体活化可将其提高到约0.5焦耳每平方米,随后的退火可以进一步提升到约2焦耳每平方米。更高的键合能量导致更快的键合前沿传播和更线性的速度曲线,但代价是由于在关键的早期键合阶段更强的粘附力拉动芯片中心而增加芯片拉伸。

图8:(a)说明了键合速度如何随更高的键合能量增加并变得更线性,而(b)量化了X和Y方向上相应的芯片拉伸增加。

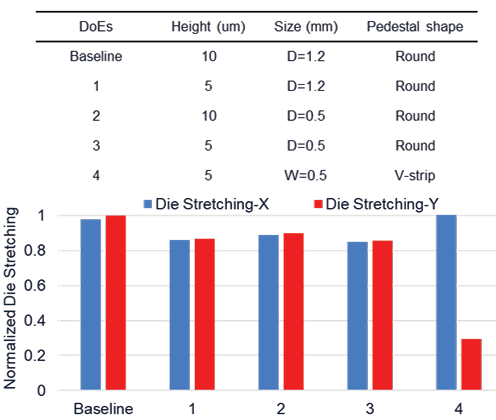

键合工具基座设计代表了影响芯片拉伸结果的另一个关键参数。比较圆形基座与条形基座的仿真显示,基座形状对键合前沿传播模式和最终芯片拉伸幅度有最深远的影响。条形基座创建更大的初始接触面积,产生如此强大的粘附力,以至于真空无法在第一阶段有效固定芯片。这导致接触后立即快速、均匀的键合,芯片拉伸方向平行于条形方向。仿真还检查了基座高度和直径的变化,发现虽然这些参数对键合传播动力学的影响较小,但更大的直径和高度都倾向于增加芯片拉伸。

图9:基座设计对芯片拉伸的显著影响,与各种尺寸的圆形基座相比,条形基座(DoE 4)显示出明显不同的拉伸模式。

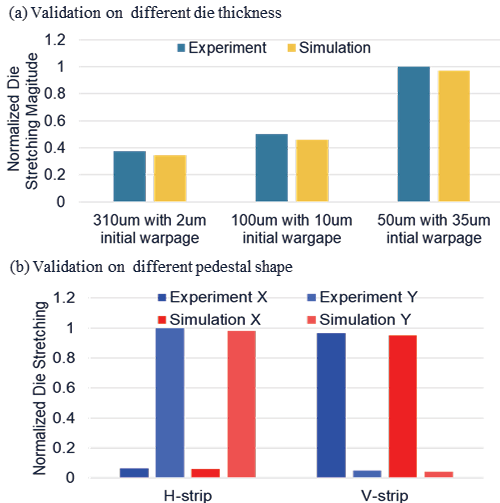

应用于更小的Chiplet尺寸

在用10毫米方形芯片验证模型后,研究人员将其应用于具有不同厚度和基座设计的6毫米方形芯片,同时保持其他参数不变。较小的芯片尺寸代表了先进封装应用中日益常见的典型chiplet尺寸。仿真结果与实验数据保持了优异的一致性,进一步证实了模型在不同芯片尺寸下的稳健性。

图10:验证了较小chiplet尺寸的模型,对芯片厚度变化和不同条形基座方向的准确预测。

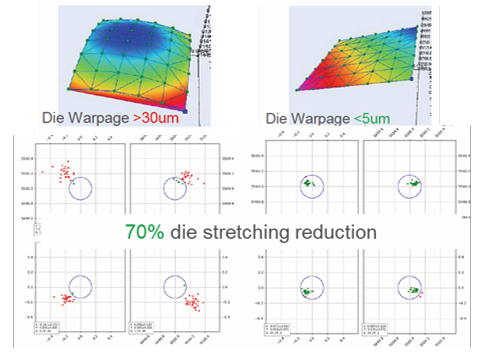

一个特别令人鼓舞的发现涉及优化上游工艺集成以减少初始芯片翘曲。通过在芯片制造过程中仔细控制各层中的应力,研究人员能够将初始翘曲从35微米减少到小于5微米。这种翘曲减少直接转化为键合后芯片拉伸约70%的减少,表明在芯片层面的工艺优化可以显著改善键合结果。

图11:实验叠层测量,表明通过将初始翘曲从超过30微米减少到小于5微米,可以将键合后拉伸减少70%,提供了强大的优化途径。

这个基于物理的建模框架的成功开发和验证为工艺工程师和设备设计师提供了强大的工具来优化芯片到晶圆混合键合操作。模型揭示了控制芯片拉伸需要仔细关注多个相互作用的参数,包括初始芯片翘曲、键合能量、真空释放时间和基座设计。通过理解控制键合前沿传播的基本物理以及每个阶段发生的机械变形,工程师可以就工艺条件和硬件配置做出明智决策,在保持可接受的产量和良率的同时最小化叠层误差。

参考文献

[1] Y. Lu, B. Pressl, K. Zheng, L. Jiang, Y. W. Wang, H. Kostner, C. Scanlan, R. Hung, and E. M. Bazizi, "Investigation of Post-Bonding Die Stretching in Die-to-Wafer Hybrid Bonding," in 2025 Symposium on VLSI Technology and Circuits Digest of Technical Papers, 2025, pp. 1-3.

来源:《逍遥设计自动化》

免责申明:文章版权归原作者所有,如您(单位或个人)认为内容有侵权嫌疑,敬请立即通知我们,我们将第一时间予以更改或删除。