为什么异构集成才是芯片未来的终局之战?

Moore定律已暮,异构集成登场

在芯片行业,每一轮技术范式更替,都是一次集体神经的震颤。曾经,摩尔定律是信仰,只要工艺不断推进,性能与成本便能双赢。但现在,我们不得不承认:摩尔定律正在退场,而系统级创新正在接棒。

Intel 在 IEEE VLSI Symposium 上交出的这份报告,就是对未来芯片版图的一次深度勾勒。报告核心一句话可以概括:

“异构集成(HI)+先进封装,是未来算力竞争的真正主战场。”

而这场战役,已经悄然开始。

01|为什么摩尔定律不够用了?

你可以不懂先进封装,但你不能忽视“封装正在变成计算架构的一部分”。

当下高性能芯片面临的几大现实困境:

· 工艺制程推进成本极高,3nm 后增益边际递减

· 物理限制导致单芯片面积受限,Reticle size 成为天花板

· IP 多样性与定制化需求日益增强,单颗 SoC 很难满足

过去我们通过“更小、更快”的晶体管来获取性能红利,现在这种线性增长已经失效。于是,异构集成登场了:通过将不同功能的芯片(CPU/GPU/FPGA/HBM/光模块等)用先进封装方式集成在一个系统封装(SiP)中,从系统层面打破性能瓶颈。

“封装,不再只是‘壳’,它是性能、功耗、成本三重优化的核心手段。”

02|Intel的“封装野心”:不造更大的芯片,而是更聪明地组合

从报告看,Intel 清晰地将异构集成推进分为三个阶段:

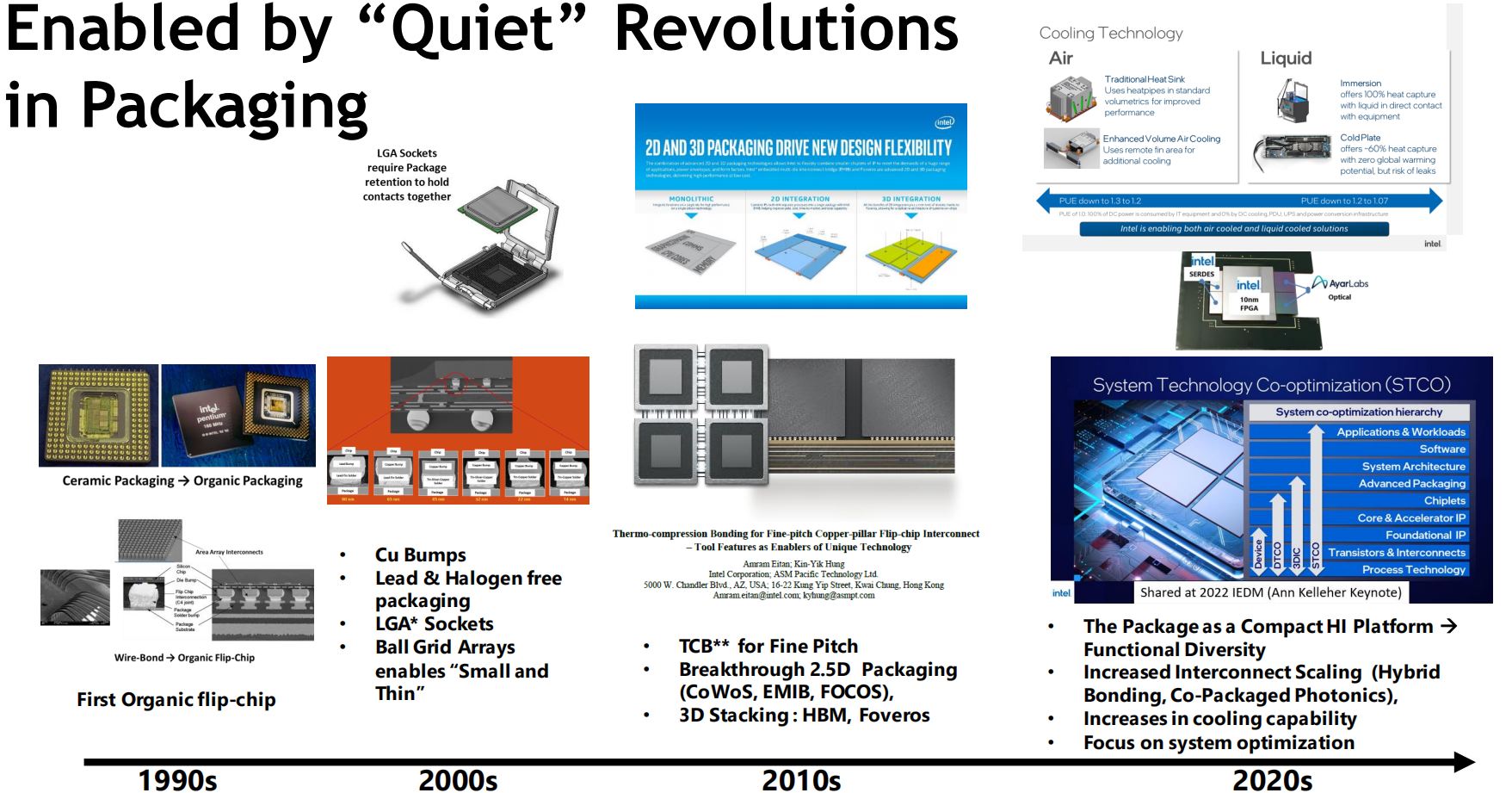

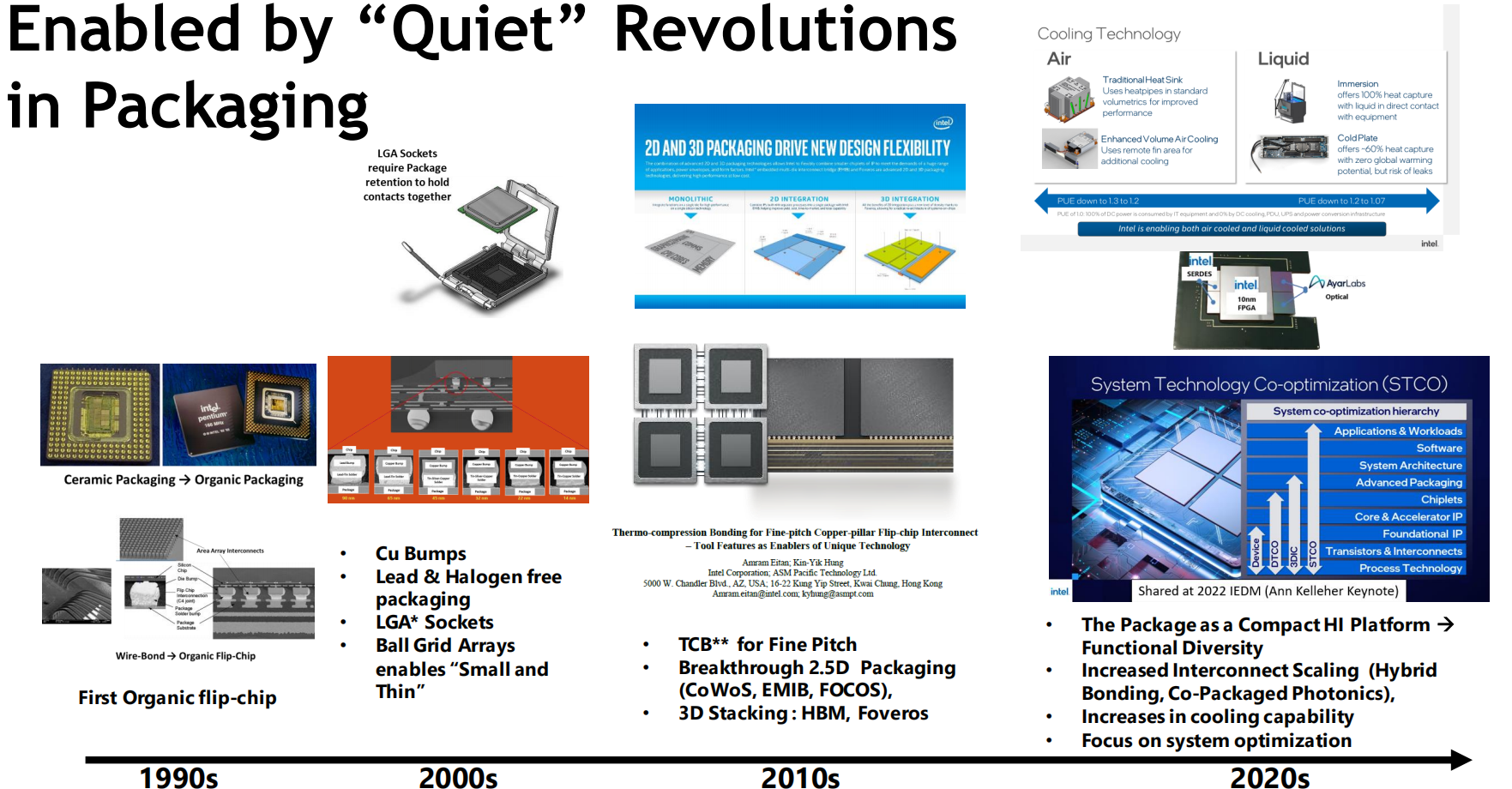

第一阶段:MCP + 封装结构演进(1990s–2010s)

· 从最早的 Flip-chip、BGA 到 TCB(Thermo Compression Bonding)

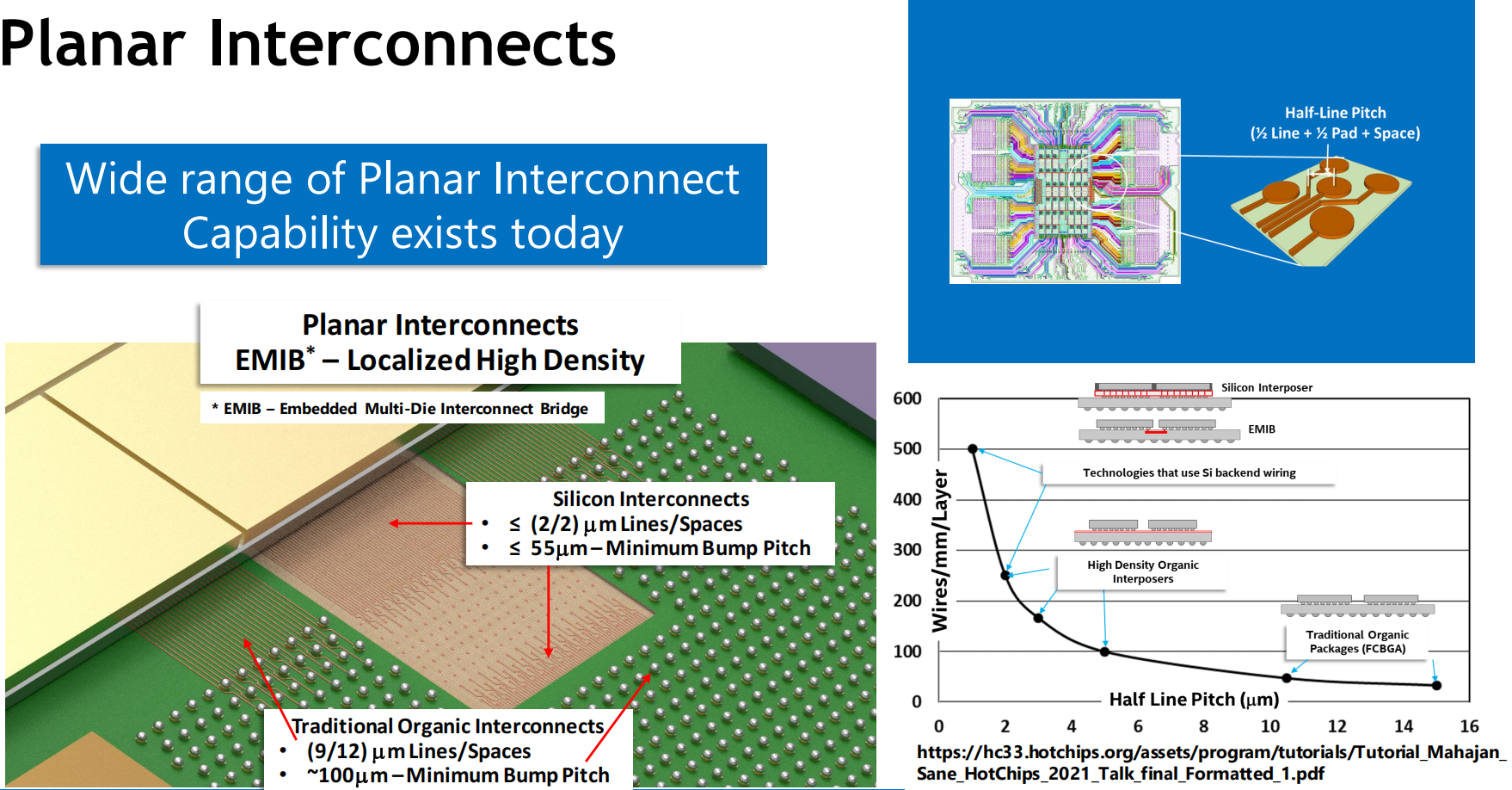

· 再到 2.5D 技术(如 CoWoS、EMIB)和 HBM

封装不再只是物理堆叠,而开始具备“电气性能设计”的角色。

第二阶段:3D堆叠 + 混合封装(2020s)

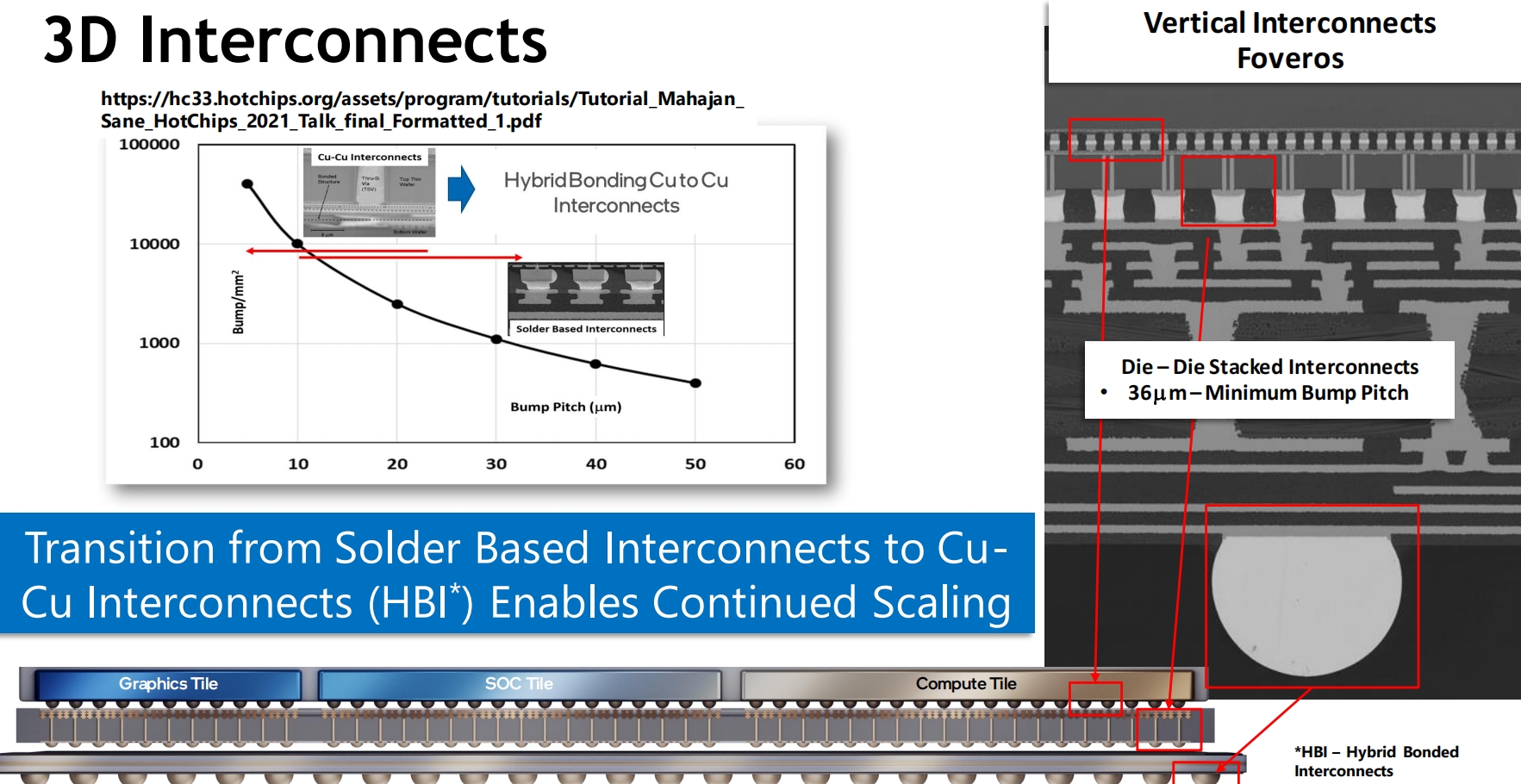

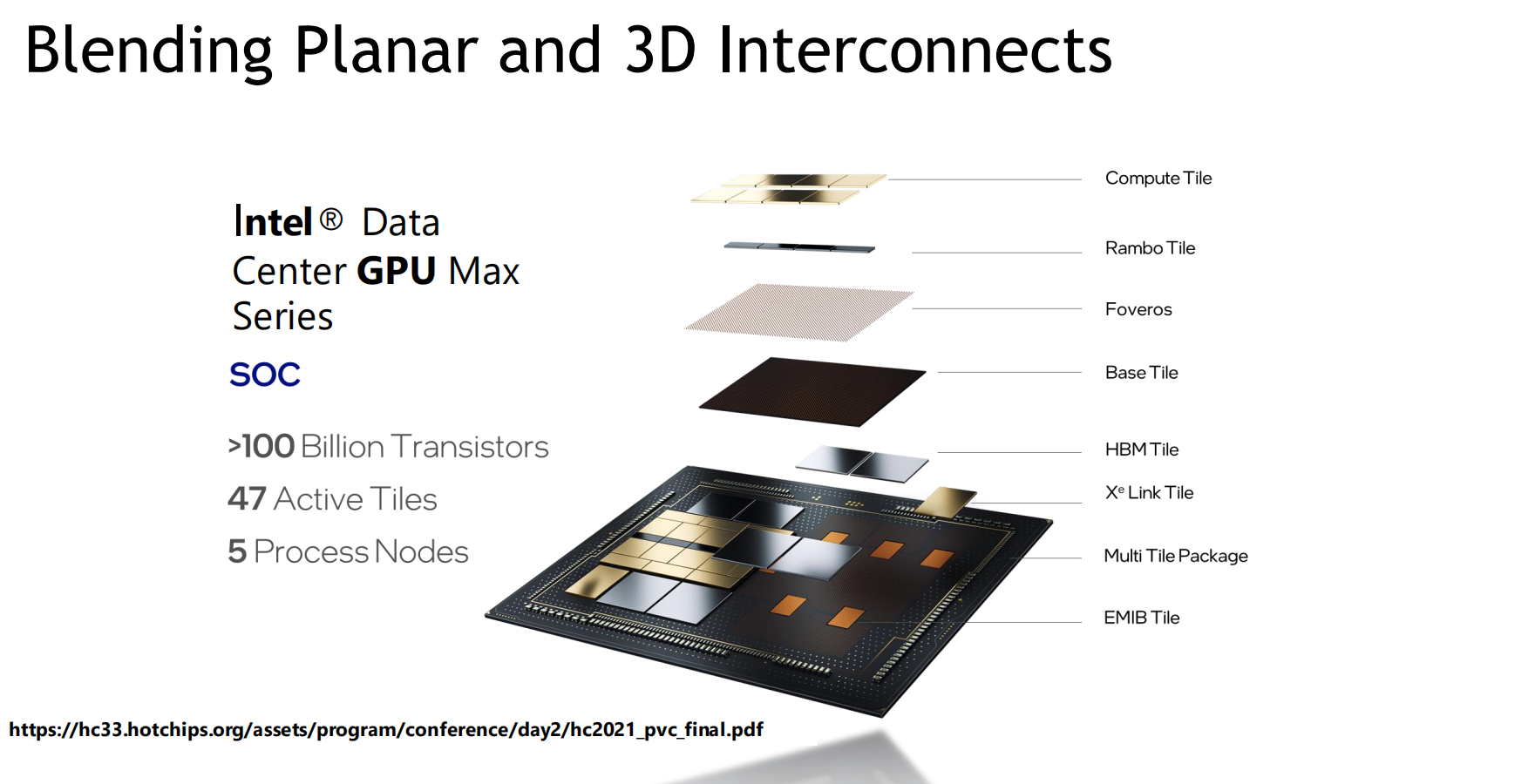

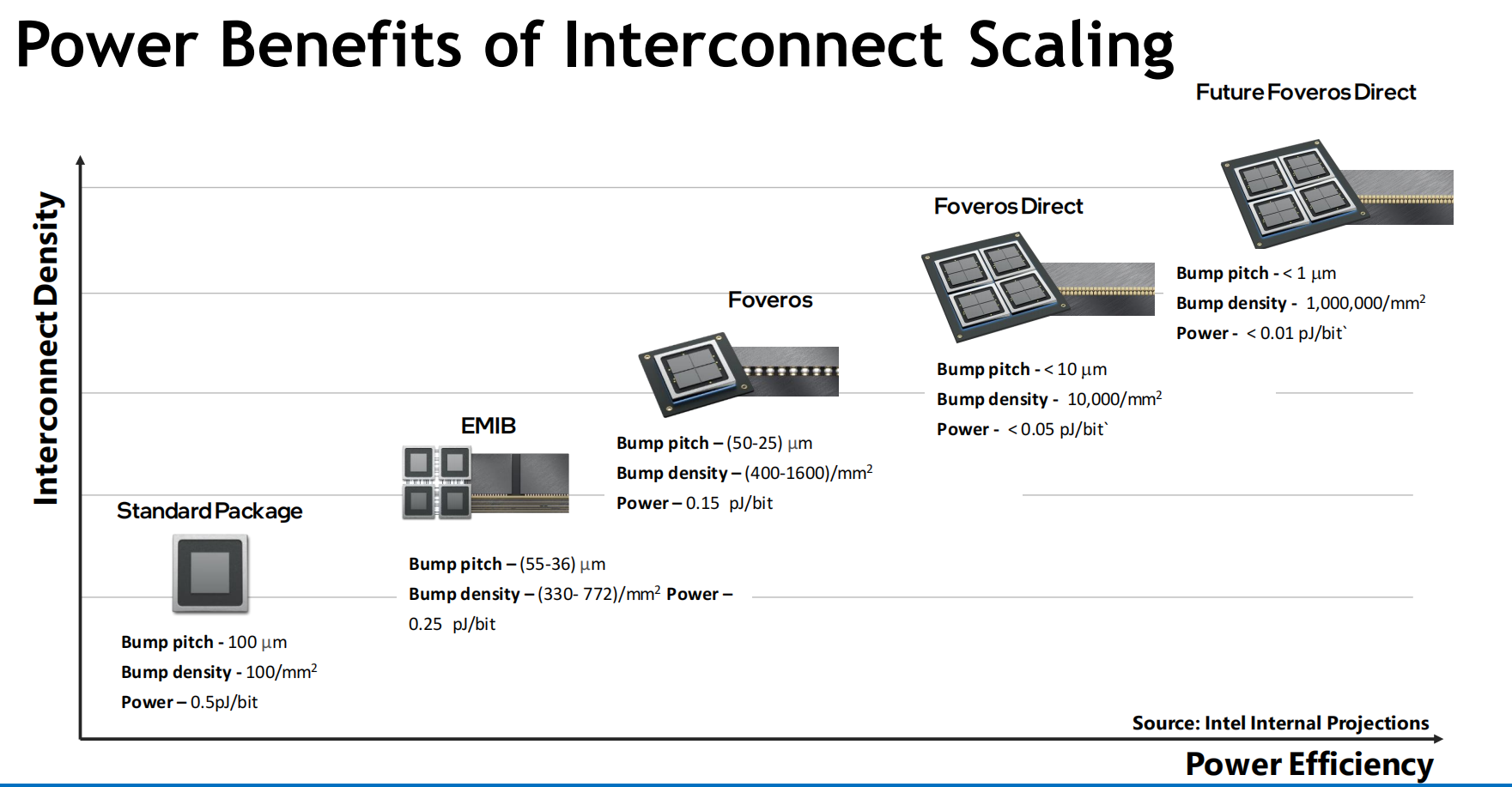

· Foveros 技术实现“垂直整合”,通过 Die-on-Die 方式堆叠功能模块

· EMIB 提供“横向连接”,解决不同 Die 的高速互连问题

· 将原本只能通过 PCB 连接的系统模块,压缩进一个封装内

“不是更小的晶体管,而是更短的连接路径。”

这一阶段最典型代表,就是 Intel 的 Data Center GPU Max 系列:超过 1000 亿晶体管,47 颗异构芯片,5 种不同制程节点的协同集成。

第三阶段:互连标准化 + 光互连 + 封装系统级设计(Now → Future)

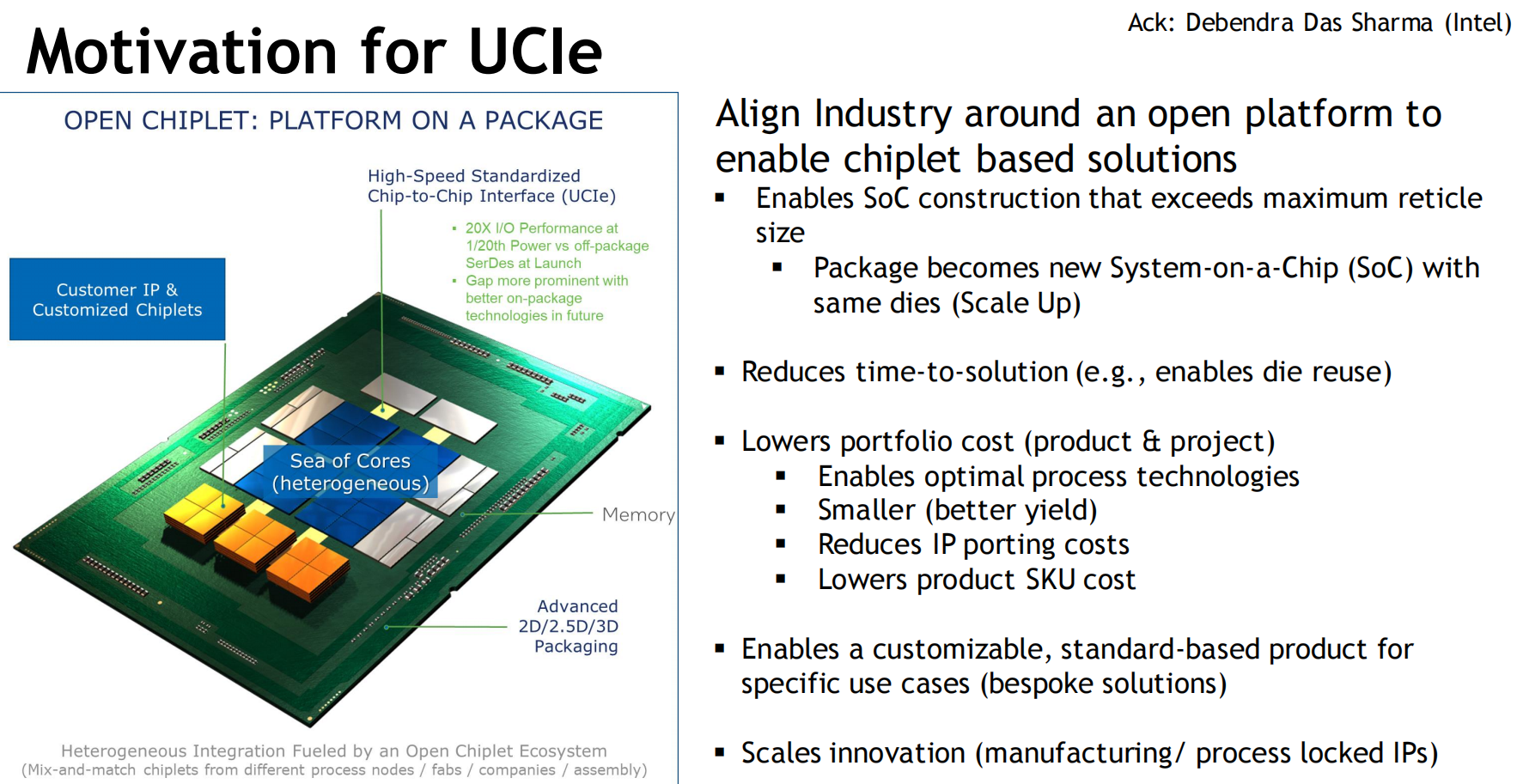

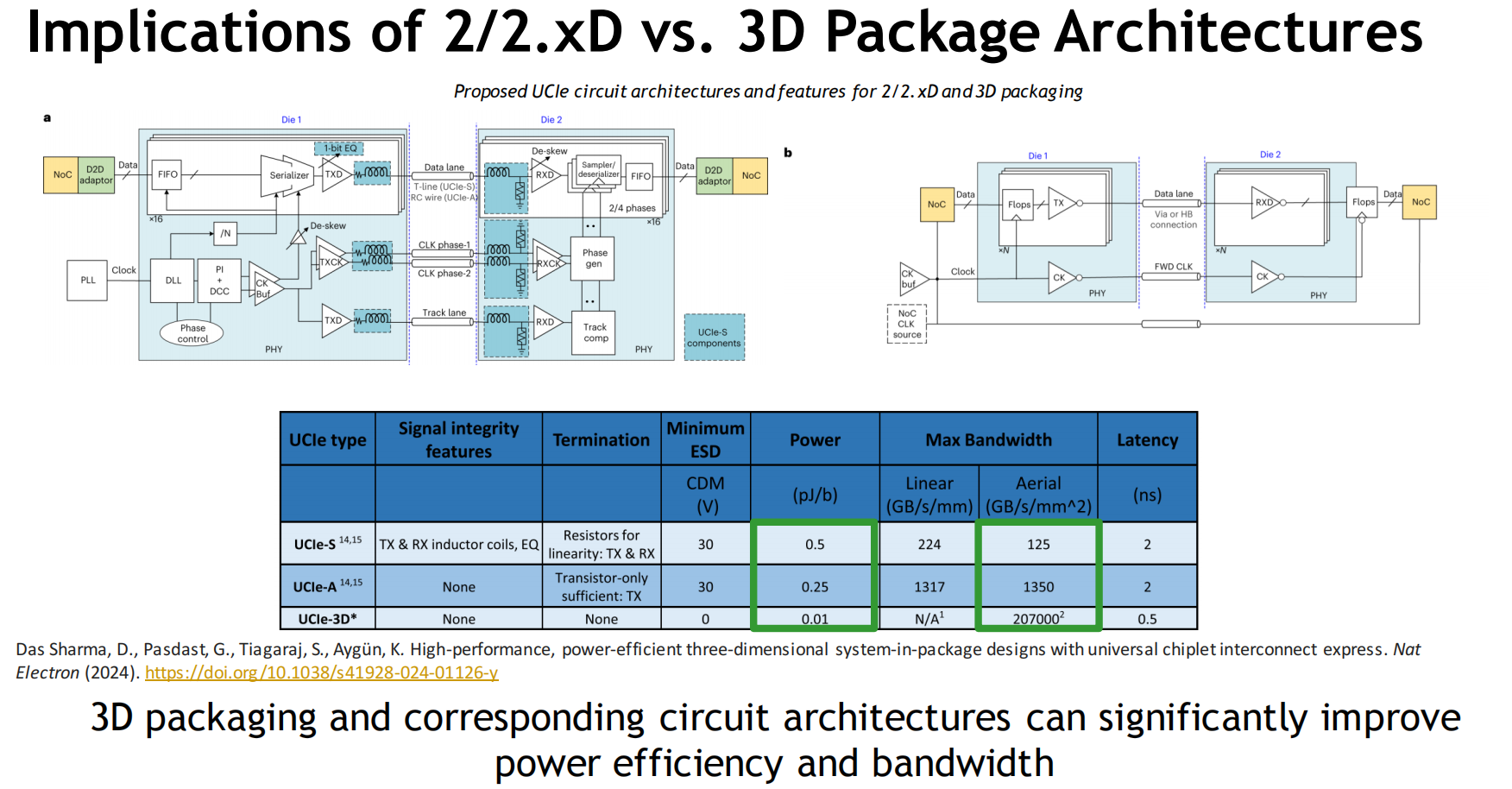

· UCIe(Universal Chiplet Interconnect Express)成为行业“通用语言”

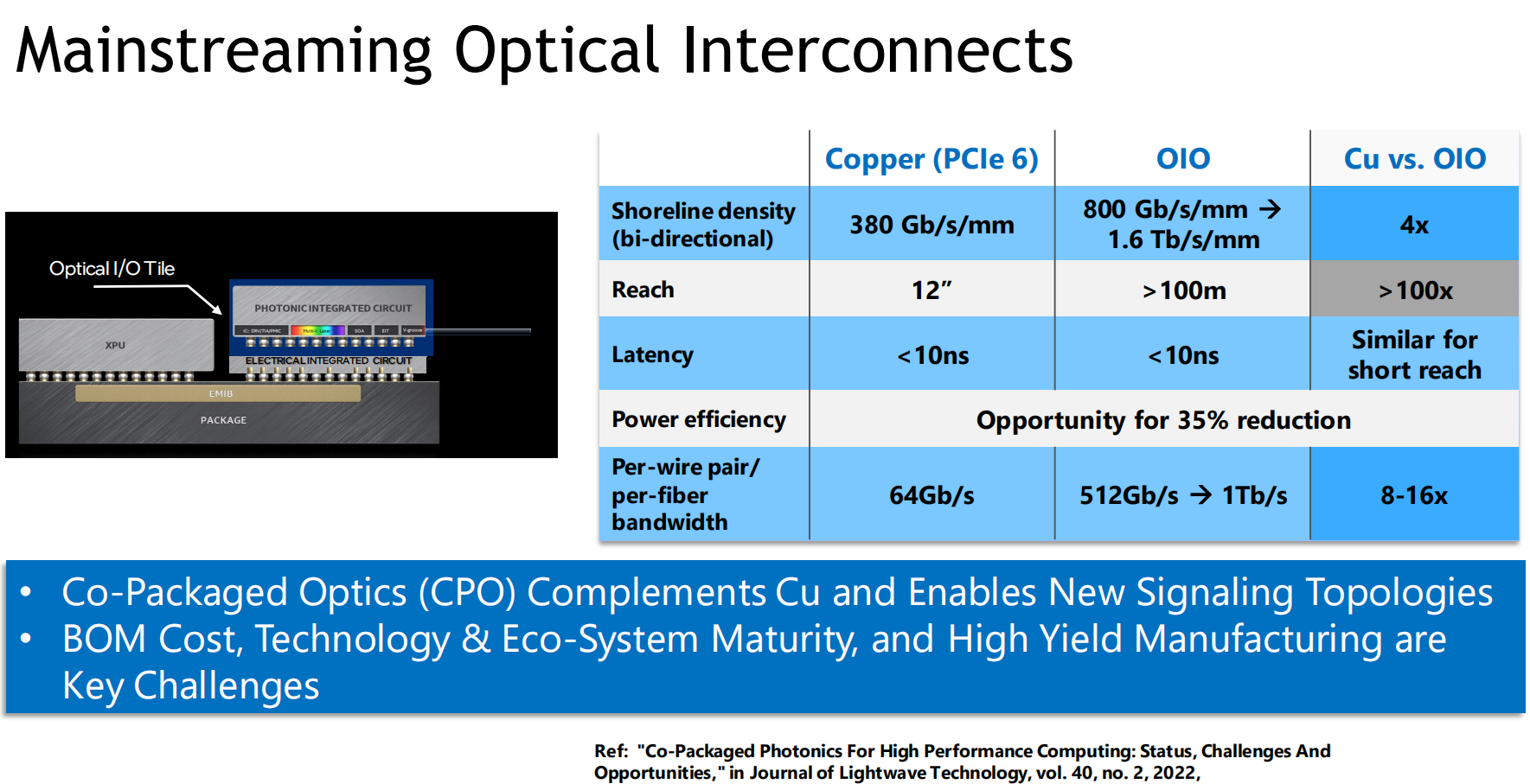

· 光互连(Co-Packaged Optics)带来带宽密度 ×4,距离提升 100×

· Foveros Direct 实现<10μm bump pitch,功耗降低至 0.05pJ/bit

这一切指向一个方向:

“未来的芯片不再是一颗芯片,而是一个‘模块化系统’。”

03|异构集成的技术细节,为什么值得行业认真看待?

我们来快速梳理报告中提到的关键技术方向,背后其实是未来五年芯片设计者必须掌握的关键词:

✅ Interconnect Scaling(互连缩放)

· EMIB(嵌入式多芯粒互连桥)与 Foveros 的 bump pitch 分别推进至 36μm 与<10μm

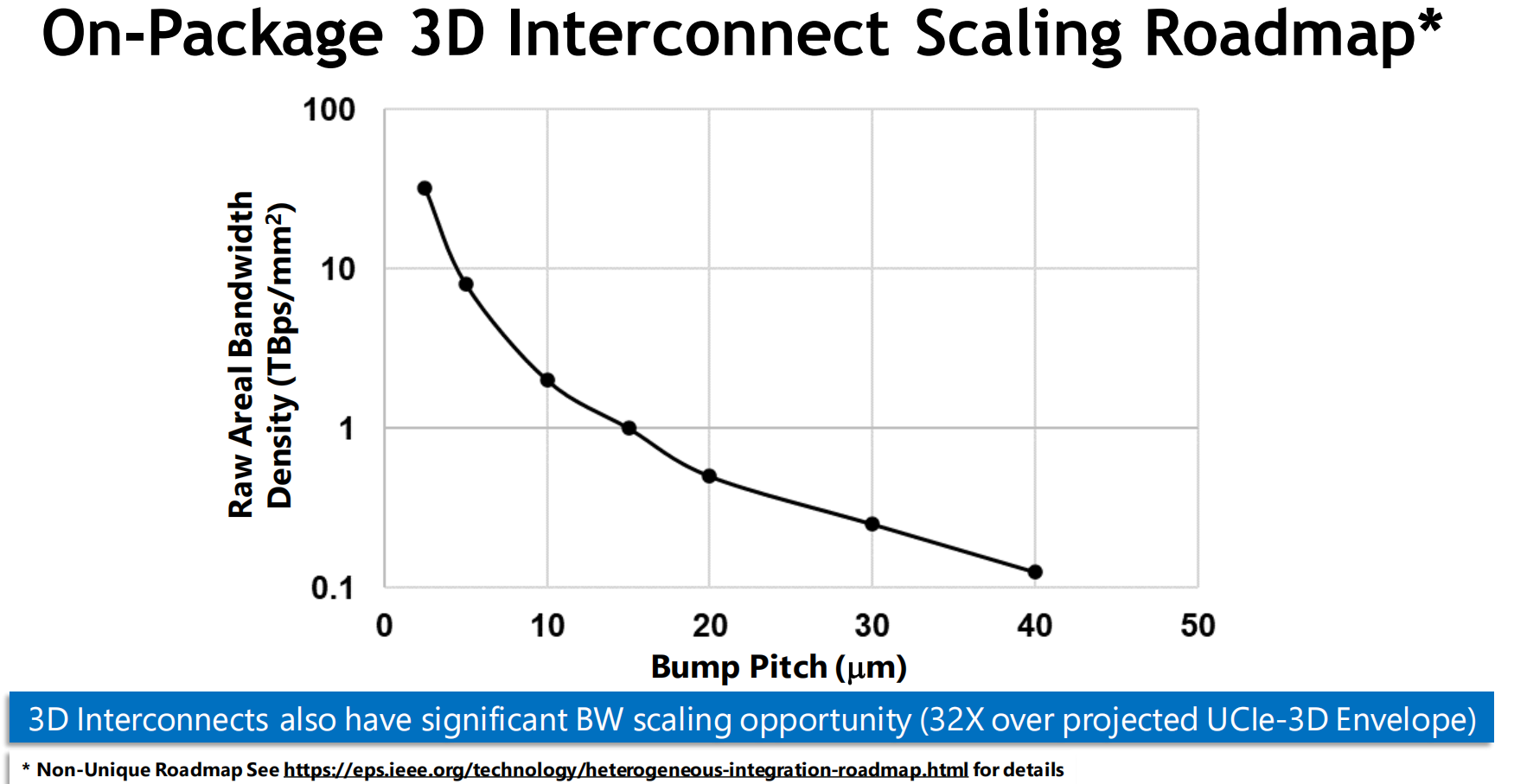

· 带宽密度上限大幅提升(3D interconnects 高达 32x UCIe-3D Envelope)

✅ Mainstreaming Optical Interconnects(光互连主流化)

· 带宽从 PCIe 的 380Gbps/mm 提升至 OIO 的 1.6Tbps/mm

· 距离从 12 英寸提升至 >100 米,打破板级互连的性能瓶颈

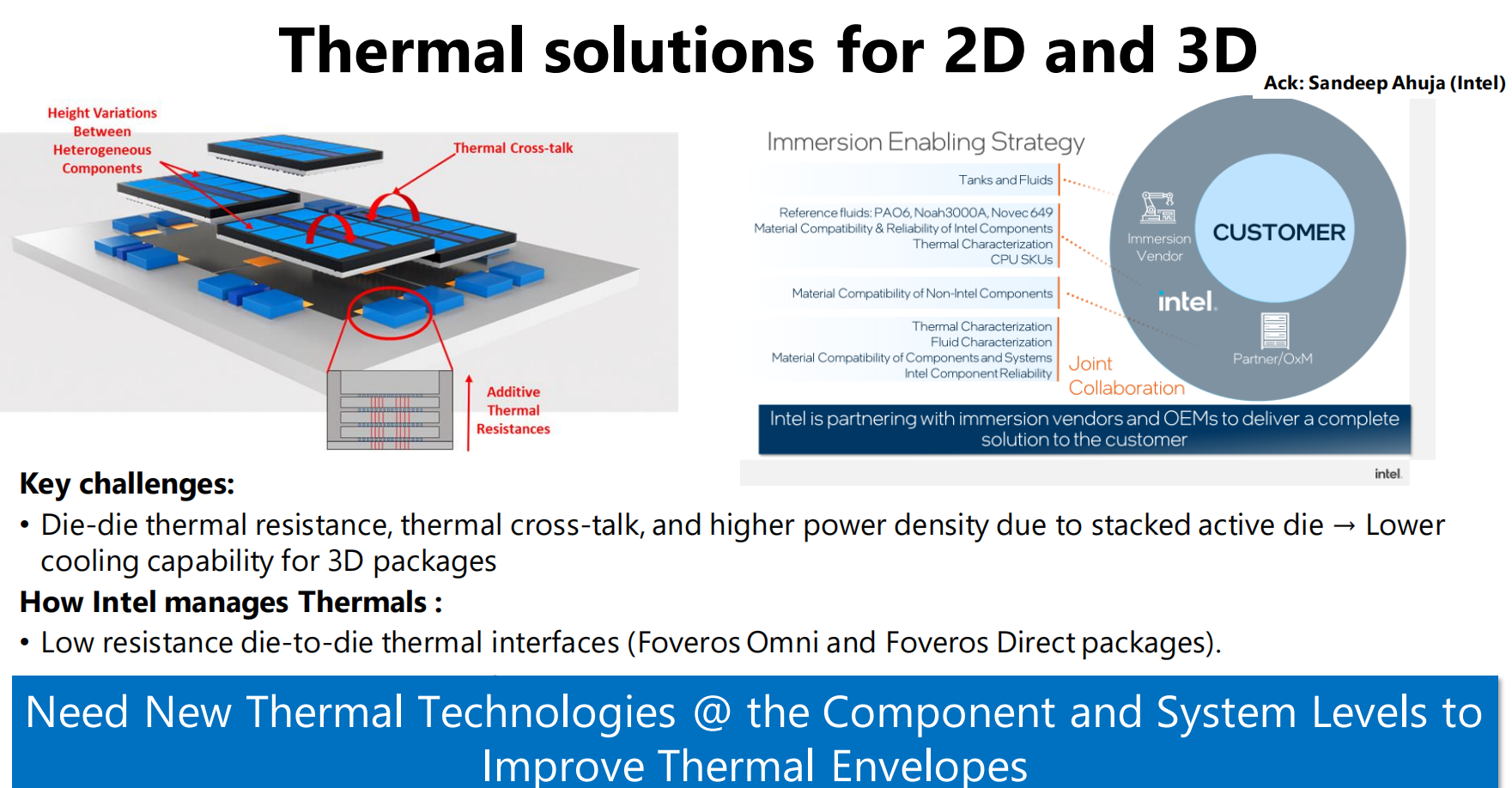

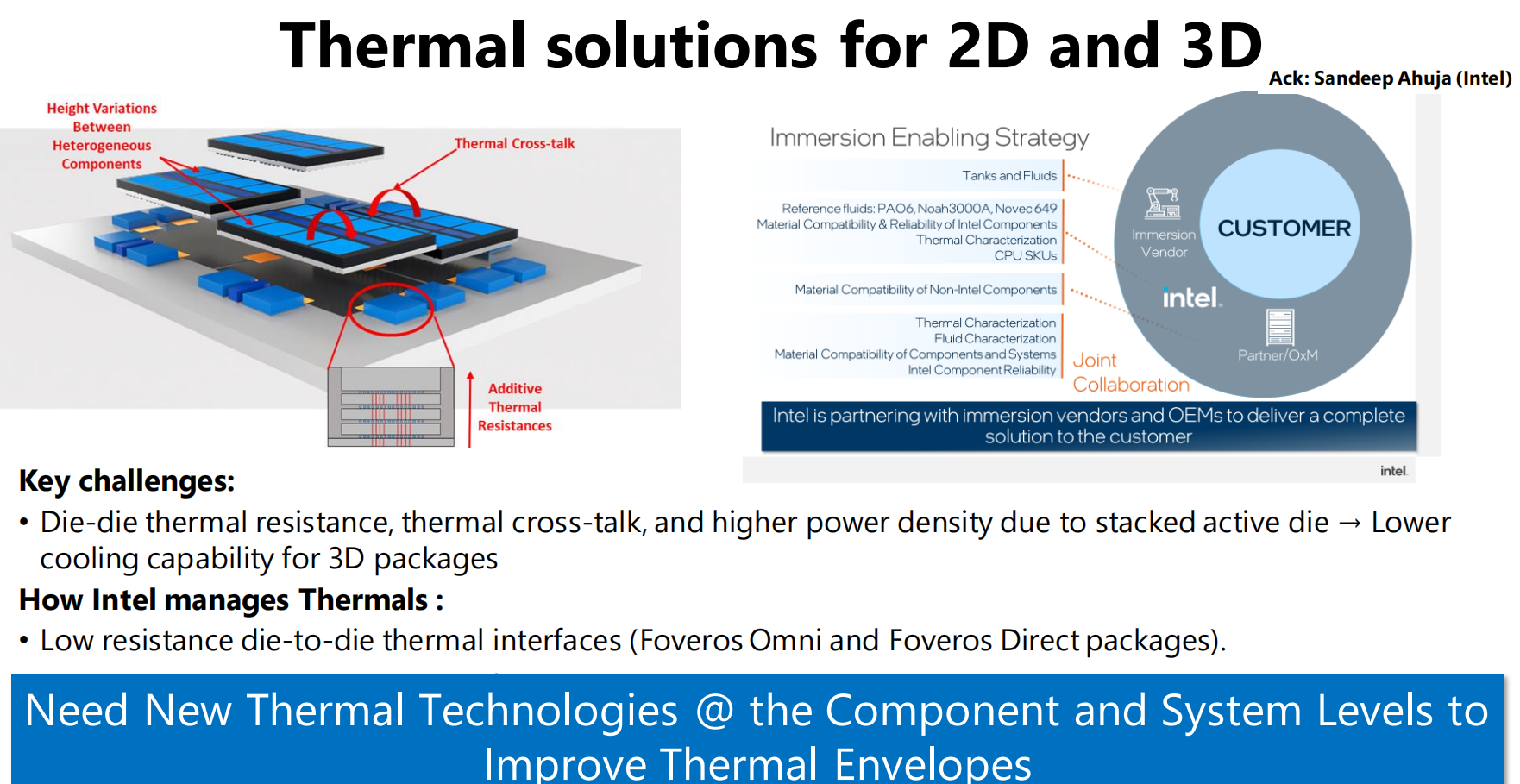

✅ Thermal & Power Delivery(热管理与供电)

· 3D 封装带来严重的“热交叉感染”,需引入冷板、浸没式冷却等系统协同优化

· Power Delivery 成为新瓶颈,需在封装层实现更高密度功率路径

✅ Yield + Manufacturability(良率与可制造性)

· 从 bump coplanarity 到 die alignment,每个环节都是影响大规模量产的关键

· Intel 强调:“封装与系统架构需要同步设计,否则无解”

“真正的创新,从不止于技术突破,更要穿透工程瓶颈。”

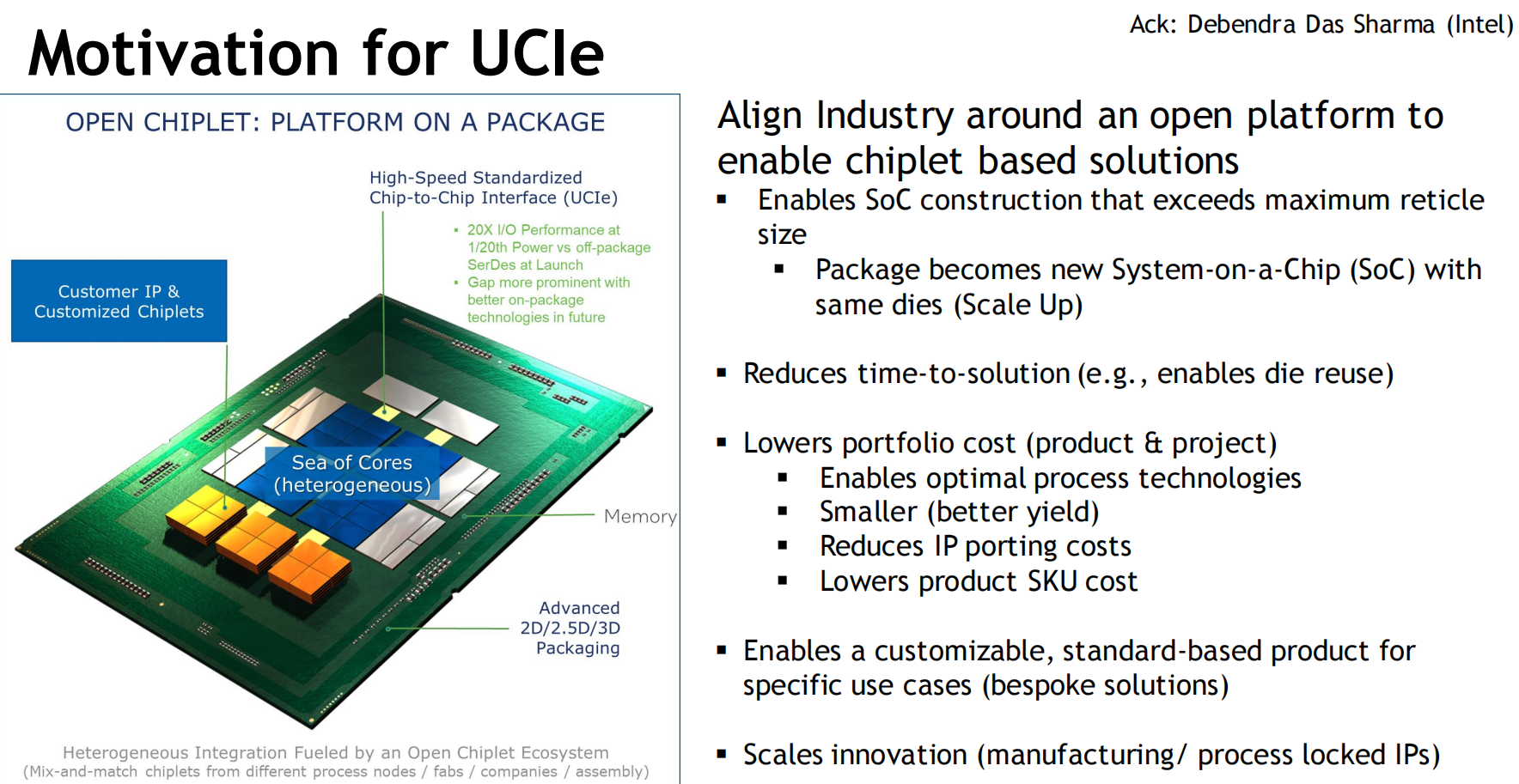

04|UCIe不是概念,而是行业集体下注

很多人对 UCIe 的理解还停留在“一个互连标准”,但 Intel 给出了更本质的定义:

“UCIe 是为了让封装变成 SoC,而不是 SoC 变成封装。”

这背后有几个深远的意义:

· 将系统集成“平台化”,让每家公司都能按需拼装自己的芯片架构

· 降低 IP 重复开发成本,让小团队也能做出有竞争力的定制芯片

· 缩短 Time-to-Market(TTM),让芯片研发周期从3年变成1年以内

这不是工程师之间的“封装标准之争”,而是:

“谁掌握了模块化的系统集成能力,谁就掌握了芯片产业的未来。”

05|结语:未来芯片是“组装的艺术”,不是单点极限

Intel 在这份报告里,并没有在制造工艺上继续画大饼,而是回到一个很理性的逻辑:

· 摩尔定律结束,性能红利靠系统级创新

· 异构集成是一种体系能力,不是一项技术

· 封装,将从“后段工程”变成“战略级角色”

正如报告最后所言:

“未来的先进封装,不只是‘能做’,而是‘能量产、能标准化、能联动’。”

来源:《半导体产业报告》

免责申明:文章版权归原作者所有,如您(单位或个人)认为内容有侵权嫌疑,敬请立即通知我们,我们将第一时间予以更改或删除。